芯片,遇到难题

最近,semiengineering的一篇文章指出,由于复杂性的不断提高,芯片制造需要更多的迭代和定制水平的不断提高,从而使设计和验证更加耗时,第一部电影的成功率急剧下降。

根据西门子提供的数据,第一次半导体流片的成功率已达到历史低点。另外,随着2nm的到来,先进工艺下的芯片良率也难以提高。

芯片遇到了很大的问题。

芯片通过率,历史低点

对ic设计而言,流片就是参加一次考试。

流片是衡量ic设计成功的关键,即将设计好的方案交给代工厂生产样品,检测设计好的芯片是否符合设计要求,或者是否需要进一步优化。如果能生产出符合要求的芯片,可以大规模生产。

在纪实片《电子立国自述传》中,流片的心情是这样描述的:每次芯片tapeout工作两三个月,我的心里就整天恐慌,难以入睡。我一直在想哪里对不对,会不会有问题...当芯片被送回来,第一次按下RESET的时候,我的情绪极度紧张,释放RESET的那一刻就是区分天堂和地狱的那一刻。

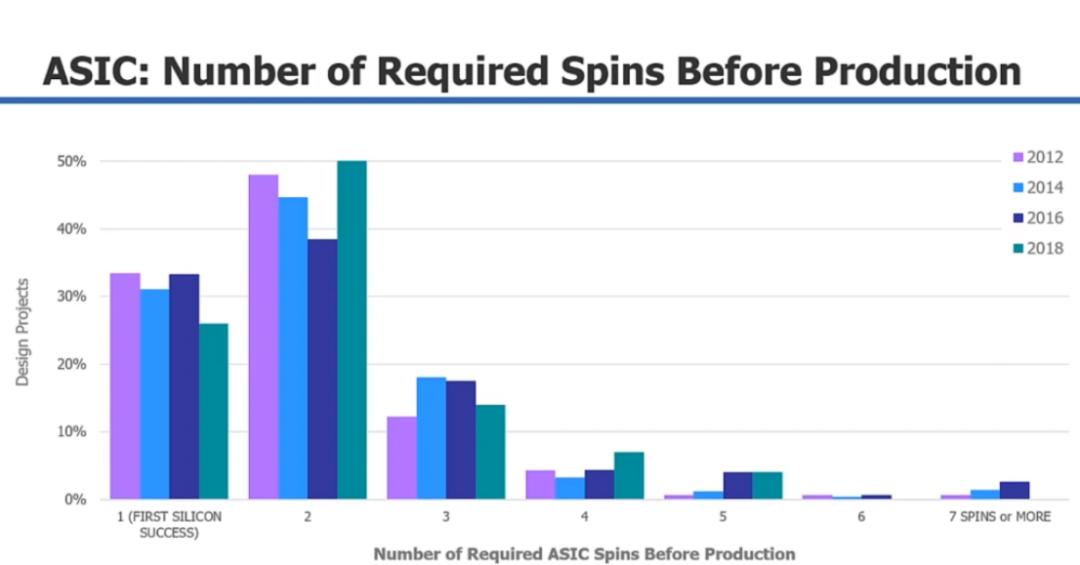

根据西门子的数据,正常芯片流片首次通过率在30%左右,但两年内降至30%。 24%,2025年通过率下降到14%,10家公司中有8家公司将失败。

有些芯片因为设计过程过于随意而失败,有些芯片因为功能问题而失败。如果流片返回后启动速度比预期慢10%,或者功耗比预期大10%,可能在市场上没有竞争力,需要重新流片。

许多芯片巨头都在流片上栽跟斗,比如AMD。 Bulldozer(推土机)架构芯片,高通骁龙810芯片等。

AMD 的 Bulldozer架构于2007 2008年开始研发,将两个物理核心组成一个模块,共享浮点单元和 L2 缓存,但实际性能没有达到预期。由于设计复杂,流片后性能差,前期研发费用浪费,而英特尔同时推出。 Sandy Bridge 结构化处理器性能更好,抢占市场份额。

高通骁龙810芯片它是2015年推出的旗舰移动处理器。但由于采用了先进的工艺和高性能的设计,流片后出现了严重的发热和高功耗问题,导致手机过热、频率降低、客户体验差。随后,高通进行了改进和升级,而竞争对手三星则以更持久、更低功耗的ExynosCpu抢占了部分市场份额。

流片通过率下降,主要有四个原因。

首先,芯片越来越复杂。如今,多芯片组件越来越多地被用于ic设计,通常需要在不同的工艺节点生产这些不同的组件。以先进的服务器芯片为例,计算核心选择5nm 技术可以实现更高的性能和更低的功耗,而储存单元可能会使用更成熟的技术。 14nm 过程可以保证成本和稳定性。它意味着需要协调多个代工厂和生产工艺,提高设计与制造的复杂性。

第二,越来越多的定制芯片。定制芯片是为特定的数据类型、算法或应用领域而设计的,这使得ic设计和验证非常繁琐。例如,定制芯片用于深度学习和推理,需要优化神经网络的特定结构和计算模式,从架构模式到指令集开发都需要重新规划。

第三,公司的发展方式发生了变化。过去,芯片开发的进度一般为18。 现在,为了保持市场竞争力,公司需要在更短的时间内推出更多的商品。许多芯片公司不得不压缩设计和验证时间,甚至在一些重要环节简化流程,以便及时完成流量任务。设计中的潜在问题无法及时发现和处理,增加了流量失败的风险。

第四,人工智能带来的压力。随着人工智能的快速发展,对半导体芯片的计算能力提出了极高的要求。AI 应用程序需要芯片提供更高的计算率,但目前的开发和验证生产力并没有明显的突破。因此,ic设计团队需要在有限的时间内交付更复杂的设计,从而增加了第一部电影失败的风险。

Briann的编辑半导体工程 在分析第一部电影通过率下降的原因时,Bailey还表示:“人工智能对芯片计算能力的需求急剧增加,远远超过了当前半导体技术和结构的进步速度。但是开发和验证技术没有跟上,工程师只能使用旧工具,在更短的时间内完成更多的工作,流片失败也就不足为奇了。

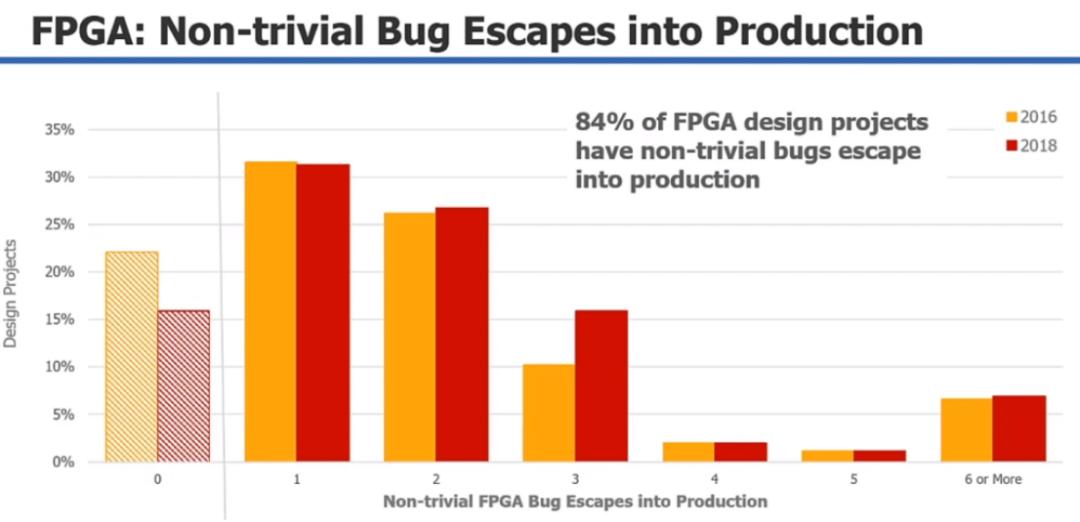

最后一次流片通过率下降还是在2018年。

2018年以前,ASIC在半导体行业的首次流通通过率也保持在30%左右,但2018年直接下降到26%。FPGA的数据很难统计,但可以看出生产中遗漏的BUG数量。事实上,2018年,只有16%的FPGA项目能够实现零BUG泄漏,这实际上比ASIC首次流通的成功率下降得更加严重。

通过率下降的节点是行业内大量设计从28nm转移到14nm的时候,当时7nm还在逐渐普及。而且越来越多的ic设计把安全作为一个关键因素,尤其是汽车和工业领域。

芯片良率,难以阻挡巨头

在芯片行业面临流片通过率暴跌的严峻形势下,即使流片成功完成,也不是万事大吉。流片只是芯片生产的开始,后续的生产环节也有很多挑战,其中芯片良率低也是一个棘手的问题,成为制约芯片行业发展的又一大障碍。

良率是半导体工厂的核心竞争优势,也被称为半导体工厂的“生命线”。

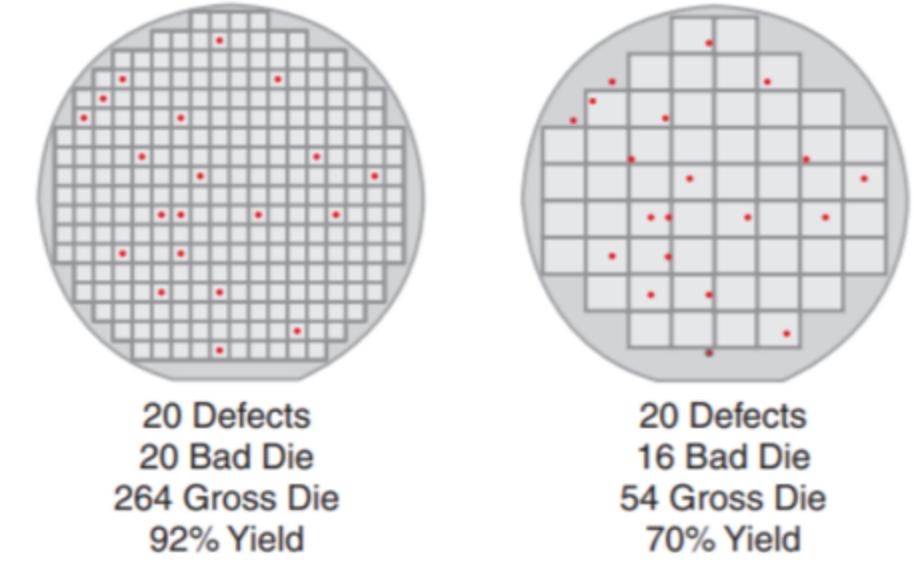

芯片良率是指合格芯片数量与生产的总芯片数量之比。也就是说,良率=合格芯片数量/生产的芯片总量。 x 100%

例如,如果在一个晶圆上生产1000个芯片,其中950个是合格的,那么良率就是:良率=(950/1000)×100%=95%

良率通常需要在整个生产过程中进行多个阶段的检测和计算,因为每个生产步骤都可能导致缺陷,影响最终良率。一般来说,在进入大规模量产阶段之前,相应的芯片良率需要达到70%或更高。

行业内,即使像台积电、三星、英特尔这样的巨头,也会受到芯片良率问题的困扰。

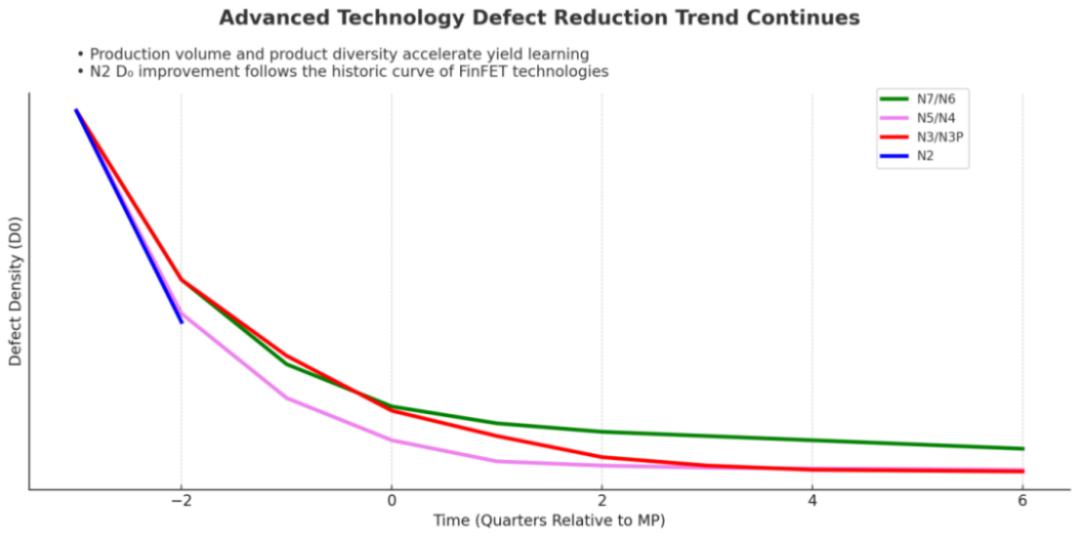

台积电在先进的工艺良率控制方面表现良好。到2020年,台积电在IEEEEEE上表现良好。 IEDM会议披露,5纳米工艺检测芯片平均良率为80%,峰值良率超过90%。

根据MSN的报道,台积电3纳米芯片良率超过80%。苹果、高通等市场巨头也纷纷选择了台积电3nm。

台积电2nm的信号更为积极。据悉,在成熟度方面,2nm工艺技术取得了长足的进步,其缺陷密度率与3nm和5nm相当。,并且采用了新的围栏极晶体管。(GAAFET)结构。增强版3nm(N3)E)与2nm工艺相比,2nm工艺的速度提高了10%到15%。现在,台积电的2nm 工艺良率已经达到 60% 以上。

相比之下,三星的情况并不乐观。2nm 工艺良率从年初开始 20% - 30% 提升至 40% 上述,Exynos是首款选择2纳米工艺的Exynos 计划在2025年11月量产2600芯片。这个和前面提到的台积电60%的良率还有差距。

3nm 工艺问题更加突出。SF3E-第一代3nm3GAE GAA工艺)良率为50%~60%之间,没有达到最初设定的70%目标。SF3-3GAP(第二代3nm GAA工艺)良率较低,仅为20%左右,远低于预期目标,导致三星在3nm芯片代工市场竞争力不足,甚至自己的Exynos。 由于良率问题,2500芯片难产。

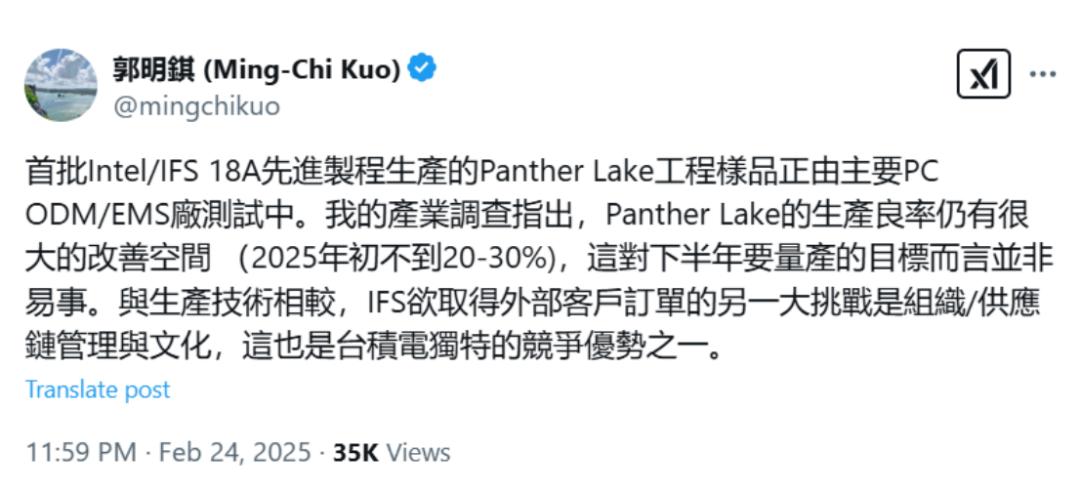

虽然有副总裁说IntelIntel在良率数据披露方面比较模糊,但英特尔表示Intel。 4 工艺良率高于预期,Intel 3 该工艺实现了整体良率和性能目标,但天风国际分析师郭明邈曾表示,2025年 年初首批 Intel/IFS 18A 制造先进的工艺 Panther Lake 工程样品的良率不足 20% - 30%。

然而,这种说法遭到了英特尔的反驳。英特尔投资者关系副总裁John 在摩根士丹利科技、媒体和电信会议上,Pitzer说:“总的来说,我们认为Intel 台积电的N3或N2可与18A水平进行比较。我们正在按计划推进Intel。 18A ,并且已经宣布将于今年上半年完成首个外部客户的流片工作。

在芯片良率方面,巨头们的困境,可见这个难题的难处。

由于多方面的原因,良率无法提高。

原料方面,硅片质量、光刻胶匀称度、掺杂剂精度等。会影响良率。比如硅片杂质和光刻胶不均匀会导致芯片性能出现问题,而优质原料不仅技术要求高,而且价格昂贵。

制造环境和设备也很重要。芯片生产需要一个超级干净的环境。空气中的颗粒可能会导致芯片缺陷。设备的稳定性、精度和维护也很重要。引进新设备成本高,可能存在技术适应问题。在生产过程中,光刻、蚀刻等过程复杂。目前工艺优化空间有限,极紫外线雕刻等新技术(EUV)同时也面临着技术和成本问题。

另外,质量控制不到位,生产过程中数据收集和分析不及时,无法提前发现和解决问题,造成缺陷难以纠正。

结语

当前芯片行业必须面对的挑战是芯片流片通过率暴跌和良率上升困难。

提高流片通过率,优化设计,可采用AI。 协同设计,提高准确性;加强设计验证,提前发现问题。同时也要注意人才培养,提高工程师的专业能力。与此同时,ic设计公司应该与晶圆铸造厂、EDA 加强供应商合作,整合产业链资源。

为了提高芯片的良率,有必要改进工艺,优化设计和工艺控制。在设备和材料方面,升级设备,选择高质量的原材料。技术创新也很重要,使用AI 以及大数据监控生产线,探索新材料、新工艺。从原材料采购到成品全过程监控,也要建立严格的质量控制体系。

解决这些问题,需要从技术、人才、产业链等方面多方面的努力。

本文来自微信公众号“半导体产业纵横”(ID:ICViews),作者:九林,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com