芯片,怎么办?

对于高性能,芯片行业有“永不满足的欲望”。

台积电的IEDM会议于去年底举行。 2 纳米逻辑平台演示成为一大亮点。

台积电N2 开发团队负责人 Geoff Yeap 在 IEDM 在座无虚席的观众面前,他们强调了代工厂 N2 平台的每瓦性能。Yeap 代表 60 多名 2 纳米平台论文的合作者表示:“技术进步不仅关系到性能。这与节能计算有关,它是移动的,AI PC 和 AI 处理的关键支柱。”

台积电在 2 选择纳米片晶体管代替纳米节点。 16 到目前为止,纳米节点使用的基础 FinFET 的晶体管。

NS 满足所有节点的平台“估计成本” PPA扩展指标(功率、性能和面积)。与以前的节点相比,速度提高了 功率提高了15% 面积增加了30% 1.15 倍。Yeap 表示,随着风险制造的进行,2 纳米技术将会出现 2025 每年年底投入大规模生产。

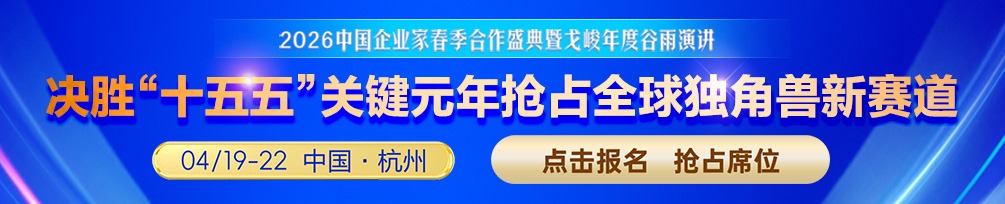

图 1.N2 具有用于 3DFabric 的 Cu RDL

需求显而易见。

“自 2023 年度第一季度生成式 AI 突破至今,AI 与 5G 先进移动和 HPC 共同点燃了整个行业对一流先进节能逻辑技术的无限需求,Yeap 表示。

NanoFlex 它是台积电的术语,是指优化混合目的性能、功率或密度的标准单元,从而实现 Yeap 所讲的“CPU 最好的组合”。“NanoFlex 它是我们用最低功耗操纵技术获得最高特性的能力。我们可以使用性能要求不高的块。 NanoFlex为了实现功率和密度目标(模块)。”Yeap说。

特别是 N2 晶体管在 0.6 Vdd 下列低工作电压表现良好。“ Vdd 下能效提高了,速度提高了。 20%。N2 技术的每瓦性能都在 0.6 V 以下低 Vdd 下面显然更好。”

Yeap 表示:“从头到尾都在进行。 3D 推广,包括铜 (Cu) RDL 层,这是以前用于台积电的台积电 这个代工厂的3DFabric( SoIC 3D 铝材堆叠技术) (Al) RDL 层次升级版本。

2 纳米开发团队提高了相互连接的能源效率,特别是在线中间。 (MoL),如图 1 显示。“通过材料和工艺的创新来改善栅极电路的电阻,提高了能源效率 线路中间有55% R 和 C(电阻和电容)减少了 20%。”

RDL 从铝到铜的金属性能更好。没有 Cu-Al-Cu,现在都是铜。”

虽然近年来 SRAM 扩展已经停滞不前,Yeap 表示 N2 平台的 SRAM 每平方毫米的密度 38.1 兆比特。与N5相比, 代为 32 Mb/mm2。测试芯片包含 GPU、Serdes 和 256 兆比特 SRAM 密度,制造时“峰值良率” 他说,95%,不需要修复。

作为“个人助理”的智能手机

台积电高级总监Lipen周日关于逻辑未来的短期课程 Yuan解释了他是如何在半导体行业的? 2030 年收入1万亿美元的观点。“每十年都会有新的创新,将行业推向一个新的水平。每一步都有一个创新,人工智能将在 2022 年底辉煌。”

“人工智能能效率为王;它正在推动台积电的所有决策。如今,能源和性能同样重要,”台积电先进技术业务开发高级总监Lipen Yuan说。

GPU 其它设备促进了高性能计算 (HPC) 发展领域,Lipen Yuan指出,人工智能服务器中使用的芯片复合年增长率 (CAGR) 为 73%。 Nvidia 的 Blackwell GPU 使用台积电 N4P(4 纳米)工艺制造,门数为 1040 一亿个晶体管,人工智能也促进了高带宽内存。 (HBM3e)、发展网络交换硅片和多芯片封装。

虽然去年(2024 年)半导体产业的大部分增长来自 HPC/AI 领域,但是Lipen Yuan表示,人工智能将成为个人计算机、智能手机、机器人和汽车恢复可观增长的动力。必须使用强大的个人计算机Cpu。 NPU(神经控制部件)对不断增加的推理处理负荷进行处理。袁征说,配置人工智能推理的智能手机将成为我们的“个人助理,学习我们独特的行为”,这将刺激我们。 2024 年到 2028 近年来,人工智能智能手机领域的增长 4 倍。

到 2030 年,90% 汽车将配备自动驾驶汽车 (ADAS) 功能。人工智能可以改变汽车的感觉,Lipen Yuan说。

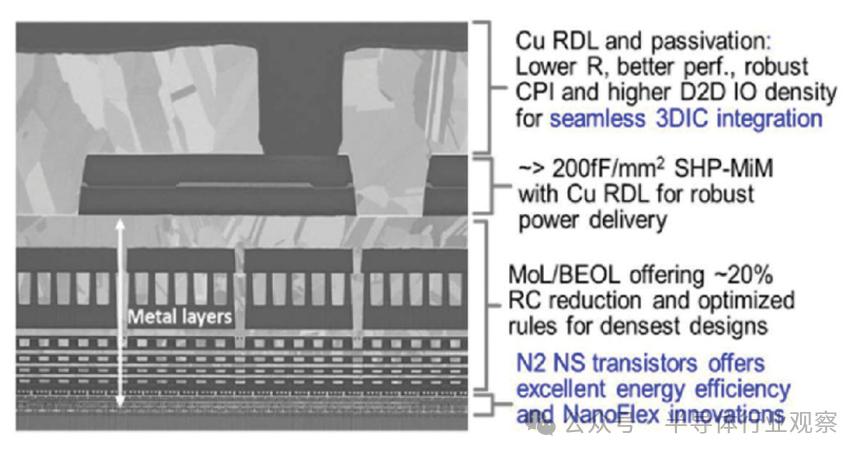

图 2. GAA 晶体管比缩放 FinFET 具有较好的可变性。(来源:IEDM 的 Victor Moroz)

FinFET Vt 变化爆发

前沿逻辑晶体管正在向全栅转变。 (GAA) 架构,由于 FinFET 能量已耗尽(图表) 2)。Synopsys 高级研究员 Victor Moroz 解释说,鳍片总宽度由光刻/蚀刻定义,1*sigma 变化量约为 0.6 纳米。他说:“这种变化可以防止标称鳍片的总宽缩小到 ~5.5 为了防止低于纳米以下, ~3.5 纳米危险(图案崩溃)区域。”

相比之下,GAA 通道厚度由更精确的外延工艺定义,1*sigma 变化量低于 0.2 纳米。另外,由于带隙扩大,“简单的量子效应”,阈值电压 (Vt) 随着鳍片总宽度的缩小而增大。 Moroz 表示,由于外延而非光刻蚀刻能更好地控制通道的厚度, GAA 晶体管的 Vt 变化更加紧密。

英特尔代工厂高级研究员 Ashish Agrawal 纳米片“从四个方向限制通道”在演讲中被指出。从某种意义上说,他说:“除了纳米片,没有扩展的空间。NS 是堆叠 FET 甚至 2D 材料通道的首选结构。

Agrawal 致力于使纳米片晶体管超过迄今为止报道的最佳栅极长度,达到以前没有报道的效果 3 纳米带通道薄而厚 (Tsi),而且不会降低电子迁移率。在 6 在纳米栅极长的情况下,英特尔研究小组改善了源极和漏极结及混合分布,以达到最佳性能和短通道效应 (SCE)。纳米带厚度控制漏极诱导势垒 (DIBL) 以及其他性能限制因素都起着重要作用。超过更薄的通道 3 nm Tsi,表面透射现象会降低传输性能。

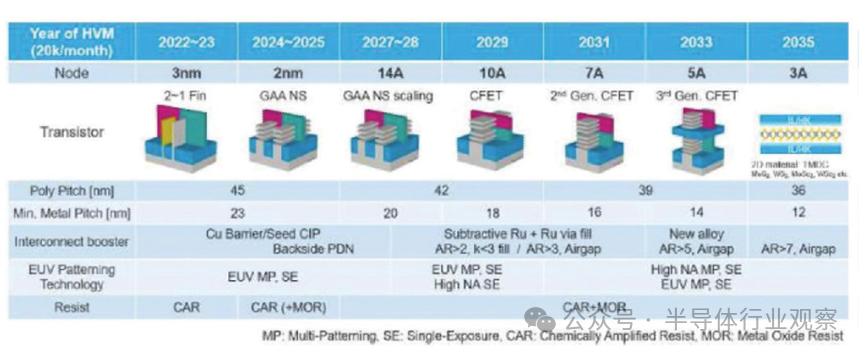

在 IEDM 事实上,台积电研究人员报告说,他们使用它们。 CFET 构建“第一个功能齐全” 3D 单片 CFET 反相器,其接触间距是行业领先的。 48 nm。"研究人员堆积如山 n-FET-on-p-FET 为了提高性能,增加设计灵活性,纳米片晶体管还具有背面接触和互连,S. Liao 说。图 3 显示了 2035 年路线图和 CFET 的引入。

图 3. 来源:Sitaram Arkalgud,TEL,在 IEDM 2024 上的演说

背面供电

对资深逻辑研究者而言,晶圆与设备的背面就像一个以前没有开发过的大陆,尽管工艺十分复杂。

比利时 imec 首席技术人员 Anne Vandooren 发表演讲,介绍了一个背面供电网络与背面接触点的演讲。 CFET 设备。使用 SOI 晶圆、晶圆键合和背面底部介电隔离 (BDI),标准单元轨道的数量从五个减少到四个。

Vandooren 表示,在低温下通过 (<250°C) 下面将媒体晶圆对准熔化键合到器件晶圆中,可以实现无间隙键合和高键合强度,从而实现晶圆背面的熔化键合。 (BS) 的访问。<250°C) 下将媒介晶圆对准熔化键合到器件晶圆,能够实现无间隙键合跟高键合强度,从而实现晶圆背面 (BS) 的访问。

CFET 优点是,随之而来 NFET 和 PFET 垂直堆叠,提高设备密度,在很多情况下使用公共栅极。在她的演讲中,Vandooren 阐述了两种不同处理过程所需的工艺步骤,其中 BDI 最好的方法性能。尽管需要更复杂的处理, BDI 该方法具有良好的隔离效果,对接触移位有较好的容忍度,并且完全抑制了基板漏电流。”

英特尔代工厂工艺研发首席工程师在她关于逻辑未来的短期课程演讲中, Anupama Bowonder 表示,垂直堆叠设备 (CFET) 增加的复杂性保证了纳米带架构在未来十年内一代一代地得到改善。Bowonder 概述了转为 CFET 测试,包括对准、键合、热预算,以及确保电子和空穴迁移率“比较”。

“对于单片 CFET(堆叠的 N 和 P),她说,并补充说,有了新的堆叠概念,行业仍然可以提高性能和可靠性,这是行业的发展方向,我们应该鼓励人们。

"摩尔定律永远存在;CMOS 缩放永远不会消失,”Bowonder 说。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:Dave Lammers,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com