当FOPLP袭击时,CoWoS的压力急剧增加。

根据台积电第一季度的财务报告预测,与过去相比,上一季度企业先进封装比例有所提高,消除了外界对CoWoS需求下降的噪音。台积电CEO魏哲家强调,台积电将继续增加CoWoS产能,以满足客户的需求。预计2025年,CoWoS的年营收贡献将在2024年增长到10%,利润将比以前有所提高。

从数据中可以看出,2024年台积电的利润超过了900亿美元,这意味着光是去年,来自CoWoS的利润贡献就超过了70亿美元,今年的利润有望通过上一段楼梯来实现。(关于CoWoS,参考文章《杀疯CoWoS》)。面对这么受欢迎的商品,其实过去一段时间有一些封装厂投入了大量资金,希望在产能紧张的时候,能够吃掉台积电的一些订单。

现在,日月光宣布,企业十年磨一剑的面板级扇出型封装(FOPLP:Fan-out panel-level packaging)决定向开设量产线的重要里程碑迈进。如果试生产成功,就可以投放市场,未来先进的封装技术恐怕不会再以CoWoS为主。

FOPLPLPL日盛的气势

近年来,半导体封装技术的流行趋势是将半导体晶片直接嵌入大型面板进行扇出封装,从而实现更高的集成度、更好的电气性能和更大的封装尺寸。与传统的封装方式相比,FOPLP可以实现更高的I/O密度,有效提高生产效率,降低制造成本。

要知道FOPLP是什么,可以追溯到扇形晶圆级封装。(Fan-Out Wafer Level Packaging,FOWLP),这种技术是英飞凌于2004年提出并于2009年开始大规模生产的,但FOWLP仅用于手机基带芯片,很快就达到了市场饱和。直到2016年,台积电在FOWLP的基础上开发了整合风扇出型(Integrated Fan-Out,InFO)A10应用处理器封装,用于苹果iPhone7系列手机,使半导体行业能够快速开发FOWLP。

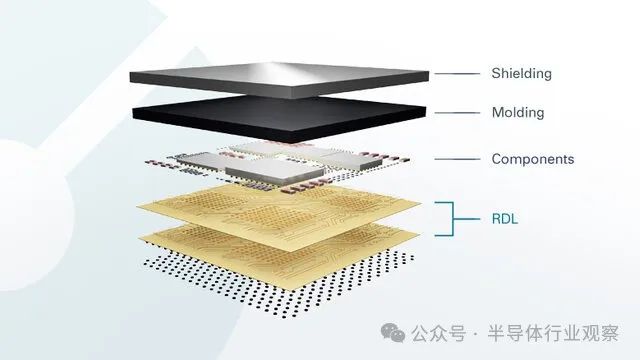

面板级风扇出型封装(FOPLP)延伸自FOWLP,同样具有I/O密度大、设计薄的特点,两者的英文简写仅差在P上。(Panel)「W」Wafer),面板与晶圆的区别,体现在尺寸和利用率上。

面板级风扇出型封装(FOPLP)就是把扇出式封装(Fan Out)面板级封装(Panel Level Package)这两种技术相结合的新型封装技术。

FOPLP具有扇出式封装的优点,使重走线层层(Redistribution Layer)当布线向内或向外时,可超过晶片大小的限制范围,使其能支持更多的外部I/O,达到高密度连接和更薄的封装,最终使商品能够以更便宜的成本达到更薄的外观。

与此同时,FOPLP还具有面板级封装的优点,不同于以晶圆为载板的晶圆级封装。(WLP),FOPLP选择面板作为封装载体,这些载体可以由金属、玻璃或其他高分子聚合物制成。在这些材料中,玻璃基板在机械、物理、光学等方面更具优势。

另外,面板级封装可以产生更多的封装尺寸,并且具有更高的生产灵活性,在面积利用率上高于95。%结果压制了传统晶圆级封装的85%,它具有生产量大、成本低、生产周期短的优点。这种成本效率水平非常显著。与圆形晶圆相比,面板封装的相对成本可以节省更多。 20%。

伴随着人工智能的到来,需要越来越多的芯片进行封装,这使得FOPLP成为大家关注的焦点。

根据Yole知名分析机构 Intelligence 风扇出型封装 2023年报告中估计,FOPLP 市场在 2022 年约为 4100 预计未来五年将出现万美元。 32.5% 明显的复合年增长率, 2028 年增加到 2.21 亿美金。事实上,他们进一步指出,FOPLP 选择将比整体扇形市场增长更快,与整体扇形市场相比, FOWLP 市场份额将在那里 2022 年 2% 上升至 2028 年 8%。这就是说,随着更多面板生产线的推出和更高的良率带来更好的成本效率,FOPLP 预计未来几年将实现增长。”

巨人们纷纷杀入其中

正是因为FOPLP的出色表现,才吸引了各大巨头投身其中。文章开头提到的日月是重要参与者之一。

日月光集团运营长吴田玉表示,由于AI芯片价格昂贵,密封设备中放置的颗粒越多,相对风险就越高。如果没有客户的大力支持,日月光不可能迈出开设量产线的大步。日月光十年前就投入了大尺寸面板级扇出型封装,他指出(FOPLP)研究开发,选择300x300方形规格,在试制达到良好效果后,推广到600x600方形规格,并且已经在去年给出了订单,相关机器预定今年第二季和第三季安装,预计今年年底试制,如果试制顺利,预定明年将送样给客户验证,然后再进行量产出货。

吴田玉认为,如果600x600良率如预期的那样顺利,相信会有更多的客户和产品导入,那么600x600有望成为FOPLP的主流规格。

台积电也是FOPLP的好推动者。去年7月,台积电CEO魏哲家亲自确认,台积电正在密集推动风扇出面板级封装。(FOPLP)该技术已经成立了专门的R&D部门和生产线,但目前仍处于起步阶段,相关结果可能在 3 年内问世。

去年年底,相关消息透露,台积电 在早期,FOPLP将选择较小的尺寸。 300×300 mm 预计最快的面板 2026 年完成 miniline 小型生产线建设。

报告指出,台积电原本倾向于 515×510 mm 与传统相比,矩形基板 12 与英尺晶圆相比,这种基板的可用面积可以增加三倍。此后又对 600×600 mm、300×300 mm 试一试规格,最后敲定初期先用。 300×300 mm整训,以后再扩展到更大的尺寸。这个决定是因为两个角度考虑了持有成本和可支持的最大光罩尺寸。

同时 FOPLP 技术还处于发展阶段,设备零部件技术还有待完善,在基板边缘翘曲运输和封装过程转换时,消耗率还有很大的提升空间。台积电选择了“先易后难”的策略,然后在未来光罩尺寸技术逐步到位后提高基板尺寸。

三星作为先进封装领域的重要参与者,也对这一技术感到敬佩。有关报道称,2019年,三星以 7850 十亿韩元(约合) 5.81 一亿美元)从三星电机手中收购 PLP 商业,这一战略措施为其当前的发展铺平了道路。

在去年3 现任三星电子半导体部门领导的月份股东大会 Kyung Kye-hyun 强调了 PLP 技术对行业的重要性。Kyung 表示,AI 半导体芯片的一般宽度是 600 mm x 600 mm或 800 mm x 800 mm,需要 PLP 这种技术,而三星正在积极开发这种技术,并与客户合作。

另外,以面板起家的群创也转移到了FOPLP封装战场。使用面板3.5代生产线,群创可以直接使用一些设备,折旧摊可以降低设备成本;而且包装基板的尺寸可以容纳6.9片12寸晶圆,也是7倍。一次处理更多的量意味着包装成本降低。其次,与传统封装相比,FOPLP的阻值更低,所以效率更好,可靠性更好,无论是电池还是大功率快充都可以派上用场。

挑战仍然落后

根据调查机构集邦调查,将使用FOPLP先进封装的商品,主要可以分为电池管理IC( PMIC)及射频IC(RF IC )、 和CPU 及GPU、AI GPU 等三类。

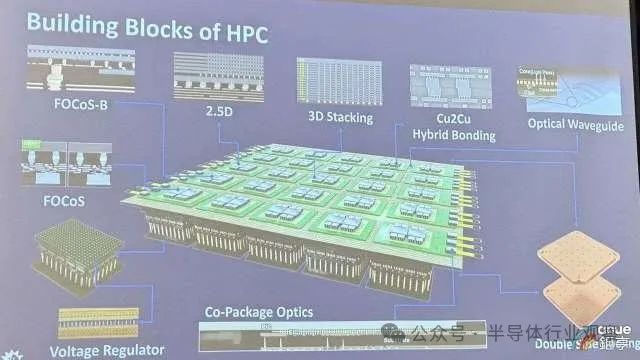

其中, PMIC及RF IC选择chip-first技术,原本主要是后期封装测试行业的深度培育。随着工艺授权商的兴起,IDM和面板行业加入并扩大了大规模生产。对于CPU、GPU及AI GPU,采用chip-last技术,由已经积累了行业经验和生产能力的封装行业开发,预计商品量产时间最早落到2026年;AI GPU采用chip-last技术,由晶圆代工业者主导,在晶粒尺寸扩大和封装颗数增加的趋势下,寻找将原有的CoWoS封装由晶圆级扩大到面板级,商品最早在2027年量产。

根据引述行业的消息,Digitimes透露,面板级风扇出型封装(FOPLP)CoWoS的生产能力有望共享。

业内人士指出,目前垂直堆叠的CoWoS封装主要用于先进工艺的AI计算芯片和AI服务器处理器的芯片封装,而FOPLP主要用于车辆和物联网的电池管理IC,主要用于成熟工艺。这两种封装技术的应用不同。

主导FOPLP发展的OSAT厂商指出,无论是510x515mmm,FOPLP之所以没有放量,是因为良率没有达到理想值,标准还没有确定。、600x600mm是一种常见的规格,目前还没有确定,这就是为什么业者还没有在FOPLP上下大力气。

报告显示,事实上,FOPLP是在2015年推出的,但因为向向, FOPLP 过渡必须投入大量新材料、工艺和设备,专门为面板级制造而定制。这些更多的面板需要精确的翘曲控制和材料一致性,以确保高密度设计中的可靠连接。上述问题使得它们无法得到更广泛的选择。

在过去的一年里,台积电因为AI芯片的需要,大大提高了CoWoS的生产能力。此前有消息称,英伟达削减了台积电的CoWoS订单,但后台积电否认了。然而,此前有消息称,由于台积电的封装供应有限,英伟达计划在服务器AI芯片中选择FO-PLP技术。

根据日月光等行业人员的良好信息,CoWoS,压力暴增!

本文来自微信微信官方账号 半导体产业观察(ID:icbank),作者:编辑部,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com