无需EUV也能造3nm芯片?AlixLabs用APS技术突破光刻垄断

在半导体行业数十年的发展历程中,每一次制程微缩都离不开光刻技术的进步。从DUV到EUV,波长从193nm缩短至13.5nm,再到High-NA EUV,整个产业链都围绕着如何用更短波长刻出更精细线条这一核心问题演进。然而,光刻技术正变得越来越昂贵、复杂且不可或缺。

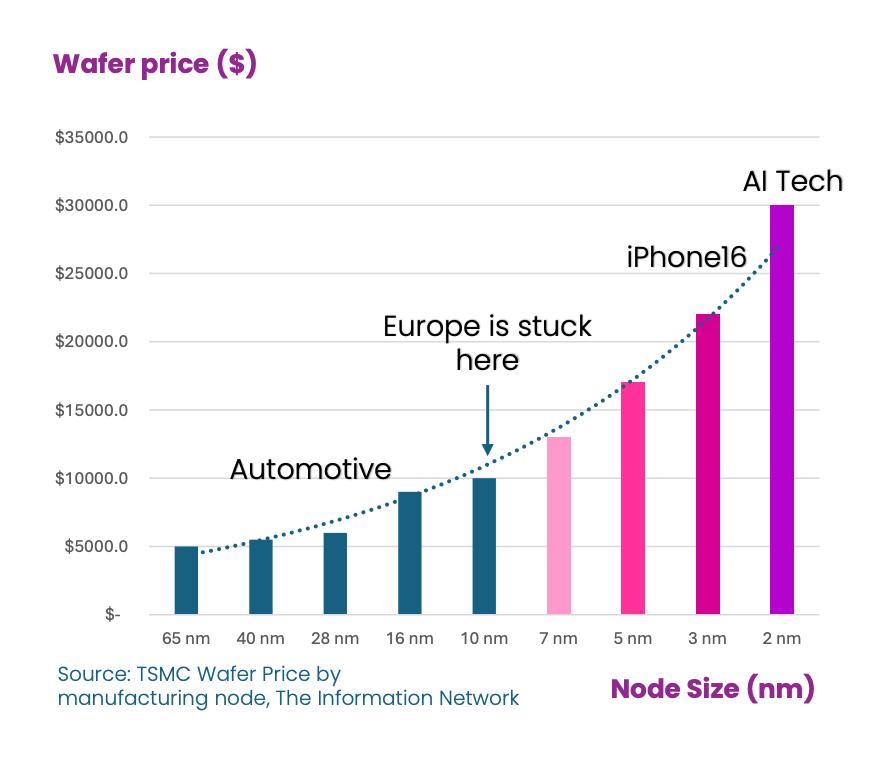

随着工艺节点不断微缩,晶圆价格直线上升,5nm/3nm晶圆单价已突破2万美元,2nm晶圆预计将达到3万美元的历史高位。价格高涨的核心原因是先进制程图形化难度极高。一台EUV光刻机价格超1.5亿美元,交付周期长达一年以上,High-NA EUV更贵,且全球仅ASML一家供应商。在AI算力爆发的背景下,这一瓶颈问题更加突出。

正是在这样的背景下,瑞典隆德的初创公司AlixLabs提出了全新技术路径:不是通过光刻刻出图形,而是通过分裂生成图形。该公司利用APS(原子层刻蚀节距分裂)技术,试图在无需EUV的情况下实现5nm甚至3nm的图形化。

技术起源:实验室的意外发现

2015年圣诞节前后,瑞典隆德大学实验室的一项普通实验意外开启了新的技术方向。

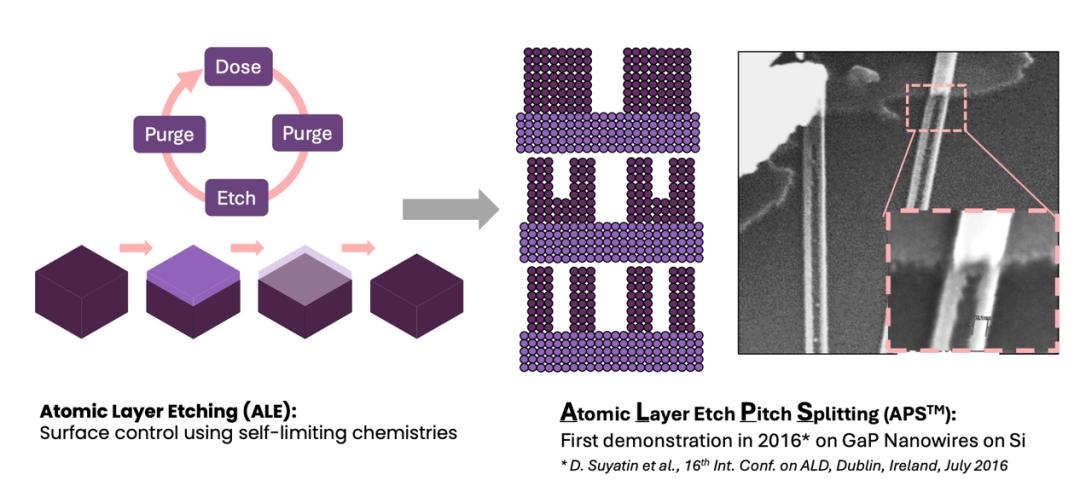

研究人员尝试缩小表面纳米线尺寸时,观察到反常现象:纳米线不仅变细,还分裂成两根更细的结构。首席研究员乔纳斯·桑德奎斯特意识到这一现象的重要性——这相当于天然的多重图形化,为非光刻微缩提供了理论可能。

原子级刻蚀将单条线分裂为两条

在EUV技术尚未成熟的时期,行业依赖SADP(自对准双重图形化)和SAQP(四重图形化)推进微缩,但这些方案导致工艺复杂度指数级增长。

2019年,乔纳斯·桑德奎斯特与联合创始人阿明·卡里米、斯特凡·斯韦德贝里共同创立AlixLabs公司,总部位于隆德,继续完善这项技术。

AlixLabs的核心技术基于原子层刻蚀(ALE)的延伸。与成熟的原子层沉积(ALD)类似,ALE也是自限制过程,但方向相反:ALD是逐层添加原子,ALE则是逐层去除原子。

这种原子级减法带来三个关键能力:一是极致的尺寸控制,每步刻蚀在原子尺度进行,使CD控制进入亚10nm区间;二是形貌自对准,纳米结构侧壁可作为天然掩模;三是三维结构保真度,相比传统刻蚀更适合FinFET、GAA等复杂结构。

绕过EUV:APS的几何突破

在此基础上,AlixLabs提出核心工艺APS(原子层间距分裂),本质是利用ALE将已有图形复制分裂,实现密度倍增。从结果看类似SADP/SAQP,但路径不同:EUV直接用短波长刻蚀成本高;SADP/SAQP需多次光刻和沉积,工艺复杂;APS通过刻蚀驱动分裂,工艺更简化。

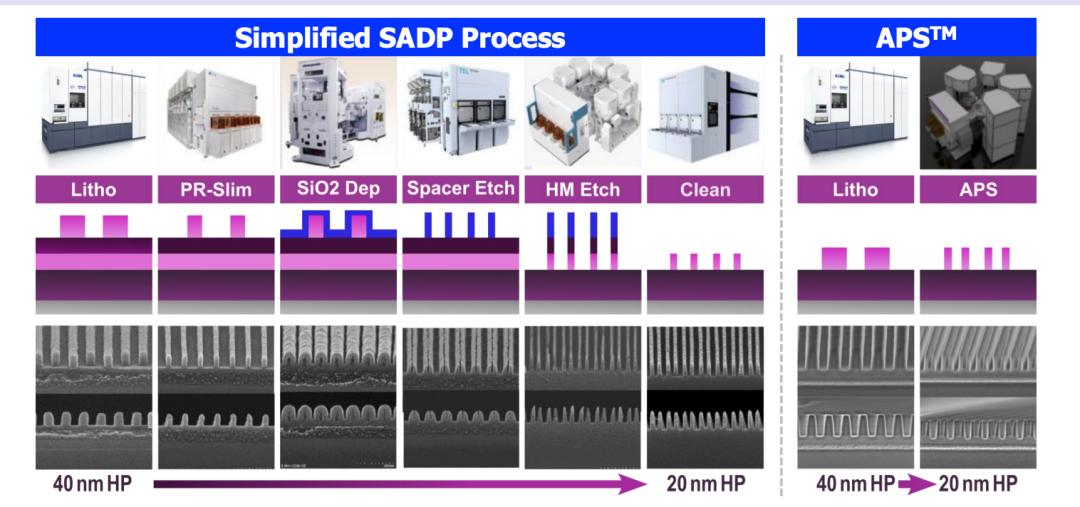

如下图所示,在实现Pitch减半(40nm→20nm)时,传统SADP需要光刻、光刻胶处理、氧化层沉积、Spacer刻蚀、硬掩膜刻蚀、清洗等多步骤,而AlixLabs技术仅需光刻和APS两步,且结构质量良好,线条均匀性和垂直度不逊于传统工艺。

APS与传统SADP的对比

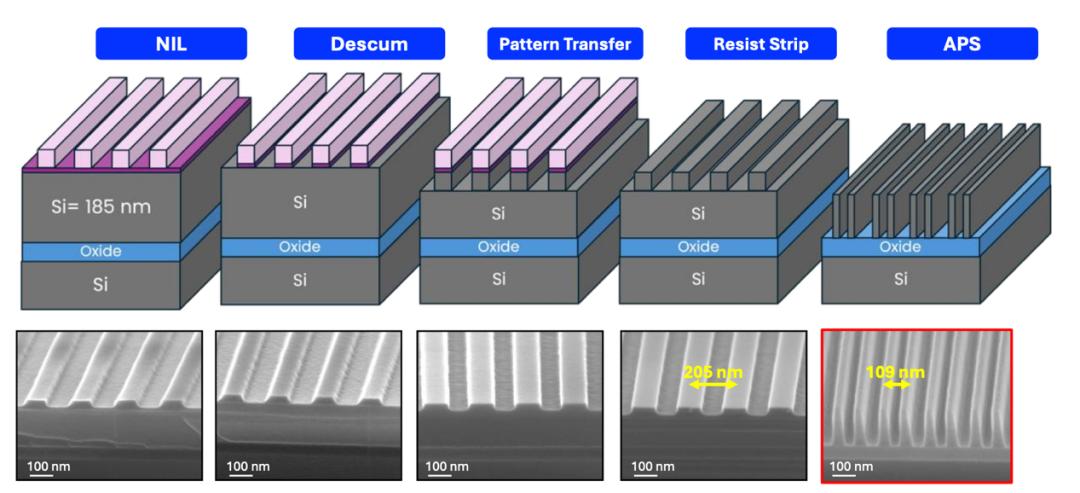

AlixLabs还演示了APS嵌入真实工艺流程的方式:NIL(纳米压印)→清理残胶→图形转移→去胶→APS。先用传统方法做出较粗结构,再用APS进行原子层刻蚀分裂,可实现从205nm→109nm的直接减半,且无需额外光刻。

APS嵌入真实工艺流程的方式

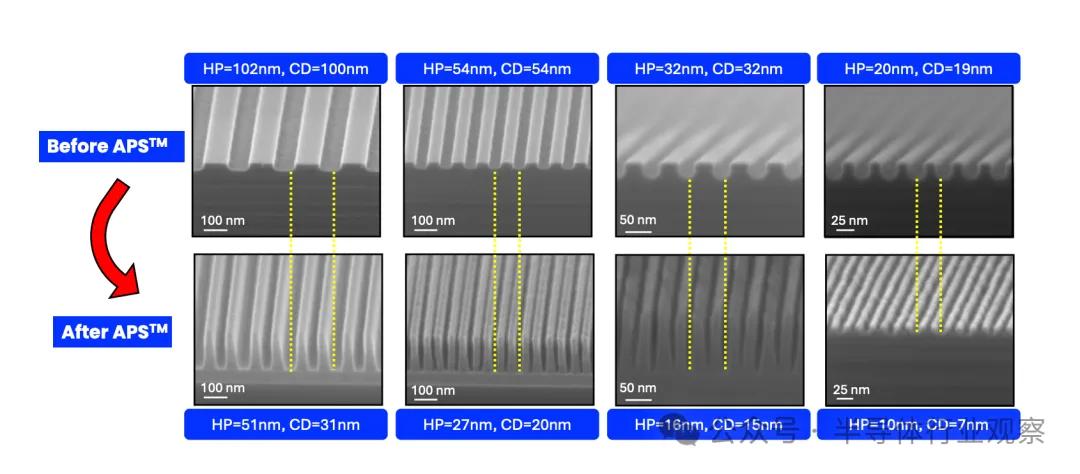

重要的是,APS并非特定节点的局部优化工具,而是普适性结构缩放技术。从100nm到20nm的不同初始间距实验显示,APS能稳定实现约2倍间距压缩,同步缩小线宽。

100nm→54nm→32nm→20nm,每一步都实现间距近似减半

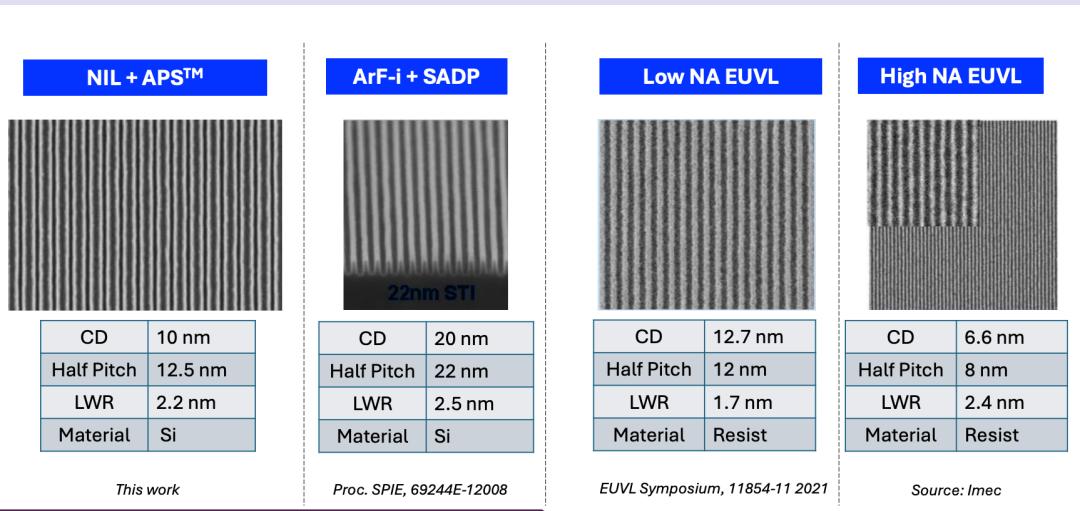

2024年,AlixLabs成功在硅基底上实现基于EBL的APS图形化,完成从化合物半导体到硅基半导体的跨越。实验结果显示,APS在硅基材料上实现10nm级CD和12.5nm级半节距,已逼近Low-NA EUV的能力范围。尽管在极限尺寸和线边粗糙度上High-NA EUV仍占优,但APS的“接近EUV性能+显著更低成本”组合使其具备成为部分工艺层替代方案的潜力。

APS与行业主流先进制程路径对比

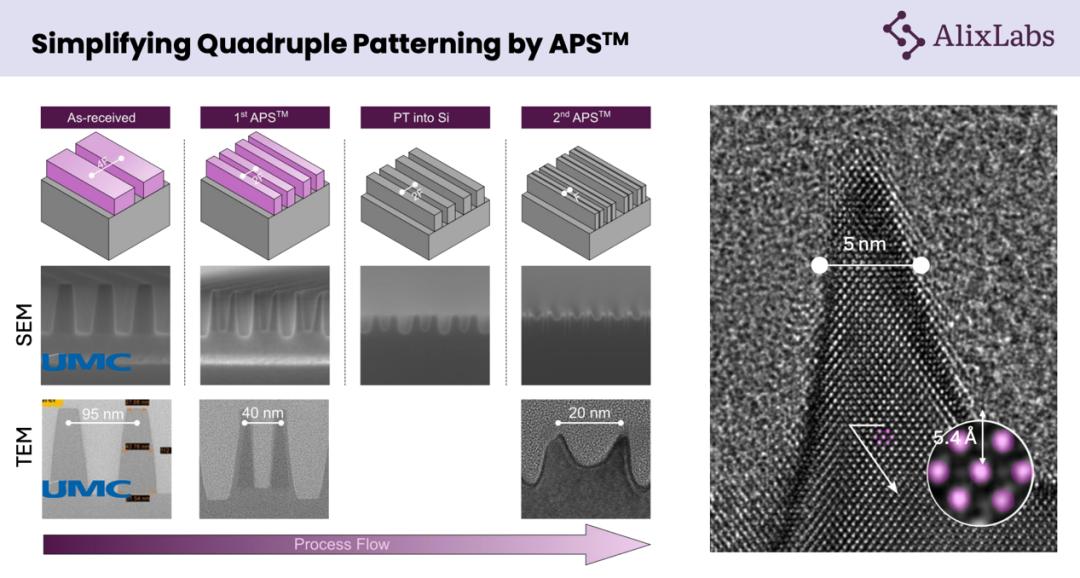

更具颠覆性的是,APS可重复调用实现层级缩放。两次APS处理可将约95nm的原始结构压缩至20nm级别,达到传统四重图形化(SAQP)的效果,但路径大幅简化。这意味着先进制程中的“多重图形化”可从复杂工艺堆叠转化为原子层刻蚀的物理过程。下图右侧展示的5nm级结构及接近晶格尺度的原子排布,表明该技术已逼近材料极限,为未来sub-5nm节点提供新可能。

APS不仅能实现2倍缩放,还能实现4倍缩放

据悉,AlixLabs已完成300mm APS设备开发,并在隆德洁净室稳定运行。

APS是纳米压印光刻(NIL)的有力补充,可扩展密集线条图案分辨率,作为SADP、SAQP和LELE等传统多重图形化技术的替代方案,具有降低成本、提升分辨率和更好可持续性的潜力。

“我们估计,APS有望将尖端逻辑和存储器晶圆的制造成本降低高达每层掩模40%,同时提高生产效率,”Sundqvist补充道。

大厂合作:产业化取得关键突破

这家初创公司与英特尔合作,近期在体硅上成功演示无需EUV的12.5纳米半间距鳍片结构,尺寸与当前3nm级尖端逻辑芯片相同。“我们的使命是打造帮助无法获取EUV设备的公司将生产规模缩小到5nm及以下的设备。通过消除对EUV的依赖,为业界提供更可持续、更经济高效的高密度芯片生产之路。”Sundqvist表示。

2025年,AlixLabs与联电(UMC)合作进行晶圆级演示,使用浸没式氟化氩(ArFi)光刻技术,成功实现19nm半节距。

根据AlixLabs2026年最新展望,APS应用已延伸到半导体制造关键领域:通过精确处理通孔(Vias)解决多层电路互连瓶颈;从硬质掩模(Hard Mask)到光刻胶(Photoresist),证明原子层刻蚀(ALE)的高灵活性。

要颠覆传统光刻模式,需配套设备支撑。AlixLabs披露的设备路线图显示商业化进程加速:Alpha级设备已可进行300mm晶圆演示,完成从0到1的突破并现货供应;具备自动化集群能力的Beta级工具将于2026年Q3交付,这是进入代工厂先导线的关键;Gamma平台针对大批量生产(HVM),目前处于概念设计阶段。

结语

对于无法获得EUV配额或难以承受其高昂成本的晶圆厂,APS不仅是替代方案,更是现实可行的“第二路径”。

当然,APS短期内不会取代EUV。对于最前沿节点,尤其是High-NA EUV瞄准的极限尺寸,光刻仍是核心工具。但在大量非关键层和成本敏感场景中,APS有望成为更具性价比的解决方案,与光刻长期共存。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:杜芹DQ,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com