或者被颠覆的芯片路线图

大家都知道,用于先进逻辑应用的芯片是从电路原理开始制造的。这个过程发生在不同的方面:从晶体管到标准单元,布局走线,直到系统设计层。构成电路原理版图的图案随后被写入光掩模。现在,这是通过使用电子束的掩模写入设备来完成的,例如可变形束 (VSB:variable shaped beam) 掩模写入机和多光束掩模写入机。 (MBMW:multi-beam mask writer)。

接下来,在光刻曝光步骤中,模具上的图案被缩小并投射到目标晶圆上方的光刻胶层上。光刻胶显影后,印刷图案通过先进的图案化和蚀刻技术进一步转移到基板底部。

预期的电路版图像在光刻曝光步骤中会出现歪曲。因为光源在光刻扫描仪和掩模版中的传播方式,会出现衍射。这一扭曲会导致图像保真度下降,即目标图像与晶圆上印刷结构的差异。后一种情况会出现一些不规则的情况,例如线距比设计值更窄或更宽,从而影响边缘位置的完整性和分辨率。所以,光学邻近效应校准 (OPC) 该技术应用于版图设计数据:它们在将图案写入掩模前对其进行校准,以最大限度地减少从设计到晶圆的误差。

在功耗-性能-面积-成本-成本-推动后续逻辑技术发展的基础上,光刻、掩模和OPC技术(PPAC)这一方面的改进尤为重要。通过缩短曝光步骤所用光的波长或增加光刻扫描仪的数值孔径,提高分辨率。(NA)来完成的。后一个例子包括从193纳米到193纳米浸没光刻的演变,极紫外线刻度(EUV)以及即将推出的0.55NA极紫外光刻(High NA EUV)。

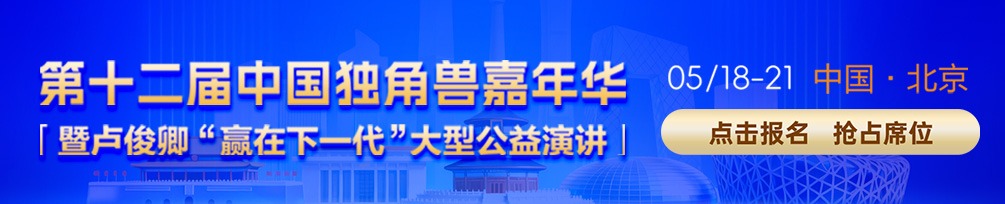

在设计上也随之发展,以跟上光刻技术改进带来的分辨率提高。随后的技术节点对间隔微缩的需求超过了光刻技术的进步。所以,先进逻辑芯片的设计从2-D 在关键层中,Manhattan布局转换为1。-D Manhattan布局(图1)。在基于2-D 在Manhattan的设计中,矩形结构用于沿垂直和水平方向对齐。相比之下,关键层中的一维设计就是沿着每一层的垂直或水平方向对齐结构。尽管1-D Manhattan的布局提供了一个集中的表达,但它也有一个缺点:当电气连接从一根金属丝到相邻的金属丝时,必须实现一个额外的层,包括大量的过孔——这增加了晶圆和电流路径的成本。

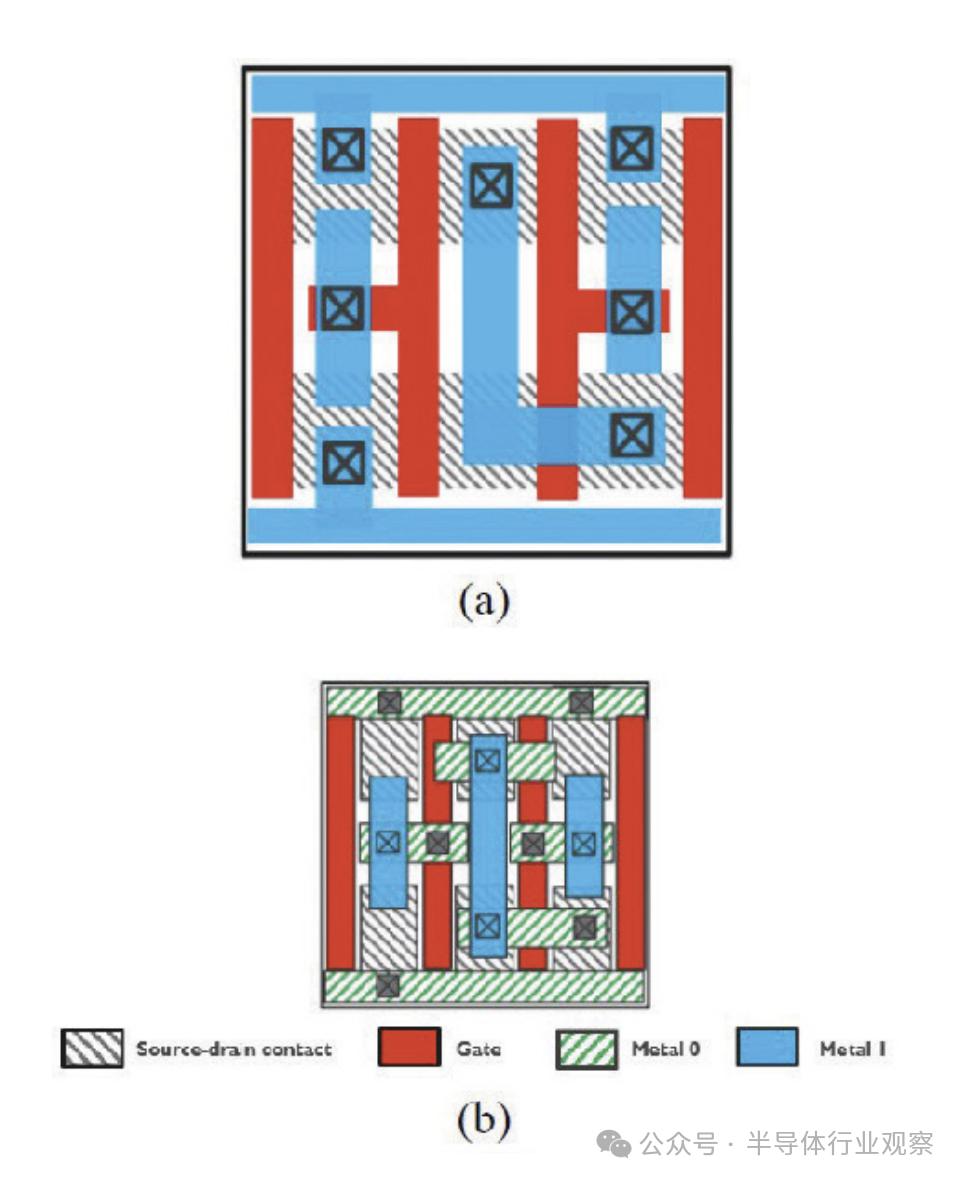

这一切,都有一个“怪异之处”:虽然今天的设计师在设计中追求矩形的曼哈顿结构,但这些结构总是在模板和晶圆上弯曲(图2)。这是模板写入器和光刻扫描仪工作模式的固有结果,分别作为电子束跟光的低通滤波器。因此,曼哈顿的设计在通过平台传输时会变得弯曲,从而在最终图案中引入额外的误差。

几年前,光刻界开始探索在光掩模上写入电路图案时引入曲线的形状。(curvilinear shapes)这个想法。多电子束模板写入工具的出现促进了这种想法,工具首次在模板上写入复杂的形状。这将有助于进一步减少从曼哈顿的设计到晶圆上曲线表示过程中遇到的偏差。

最近,业界也考虑使用新的OPC算法,将曼哈顿的设计版图调整到更复杂的模板和晶圆上的曲线形状。传统的OPC和反向光刻技术(ILT:inverse lithography technology)作为改进光刻步骤工艺窗口的一种方法,里面的新型“曲线”OPC技术开始出现。

最近,曲线掩模和OPC技术已经成为半导体行业的热门研发课题,2025年 这也反映了SPIE先进光刻和图形会议投稿数量的不断增加。

曲线(Curvilinear)在曼哈顿电路原理的基础上,OPC和掩模策略仍然存在。下一步,imec建议在设计阶段引入曲线几何结构和路径( curvilinear geometries and paths),它的优点远远超过了曲线OPC和掩模策略,是一个创新的概念。与目前的路线图演变不同,曲线设计有望在提高电气性能的同时,降低晶圆制造成本,实现技术节点过渡。所以,正如imec在2025SPIE先进光刻和图案化大会上所展示的那样,它有望彻底改变半导体产业。通过三个用例,我们展示了它的优点。

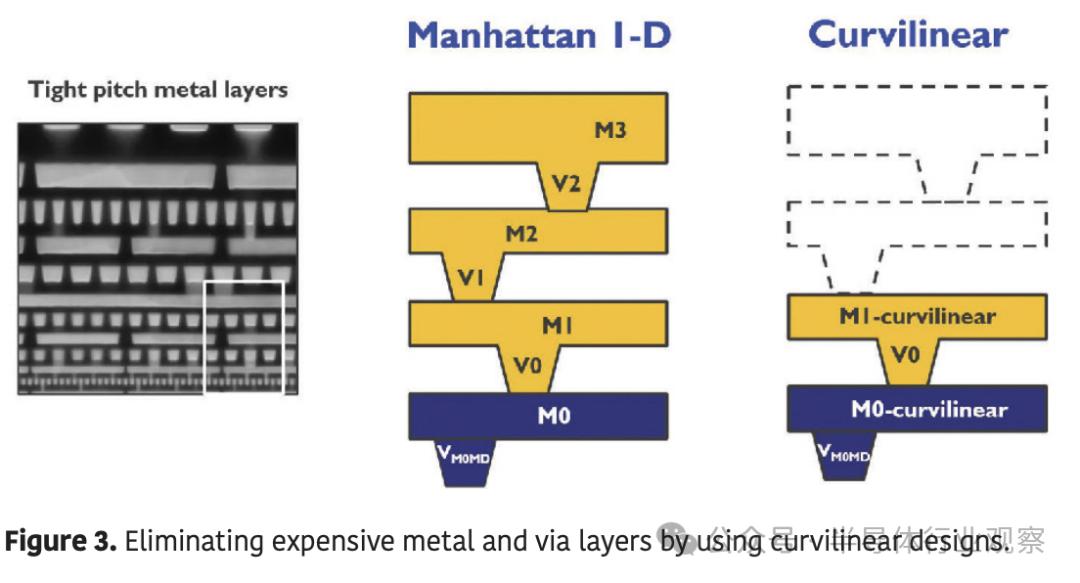

用例 1:中段中段通过曲线设计简化 (MOL) 与后端 (BEOL) 层及过孔

首先证明曲线设计有利的例子是标准单元的走线训练和金属层紧密间隔的规划走线设计。

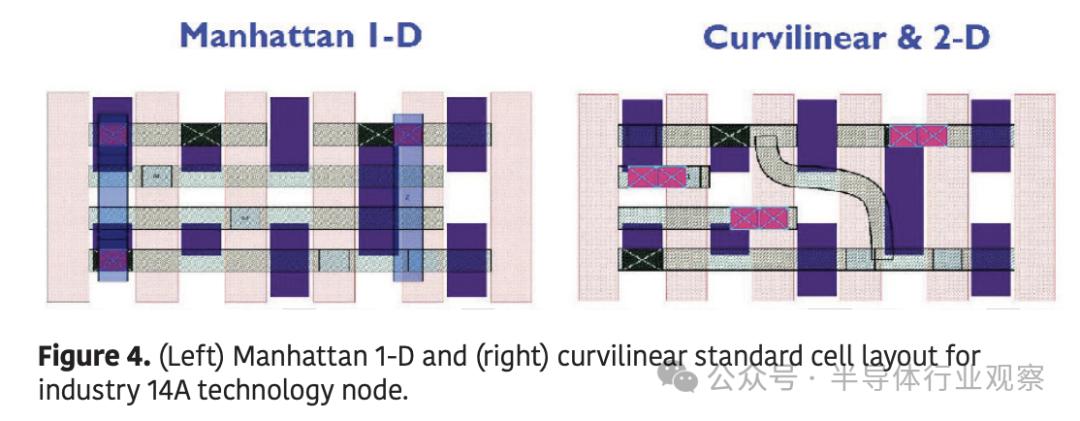

对14A或以上晶圆代工厂来说,在标准单元和紧密间隔金属层中选择曲线设计,可以合并最昂贵的MOL和BEOL层,从而减少所需金属层的数量,从而消除相应的过孔(图3)。模拟表明,如果曲线设计能顺利去除M2和V1(一层金属层),晶圆成本可降低7%,晶圆厂周转时间可缩短5%,工艺步骤可降低7%。Imec的研究人员还评估了这一特定用例对电气性能的影响:与标准单元级曼哈顿1D设计相比,曲线设计的性能提高了5%左右(图4)。由于避免了额外的过孔,缩短了电流金属路径,所以性能提升的指标是延迟时间的减少。

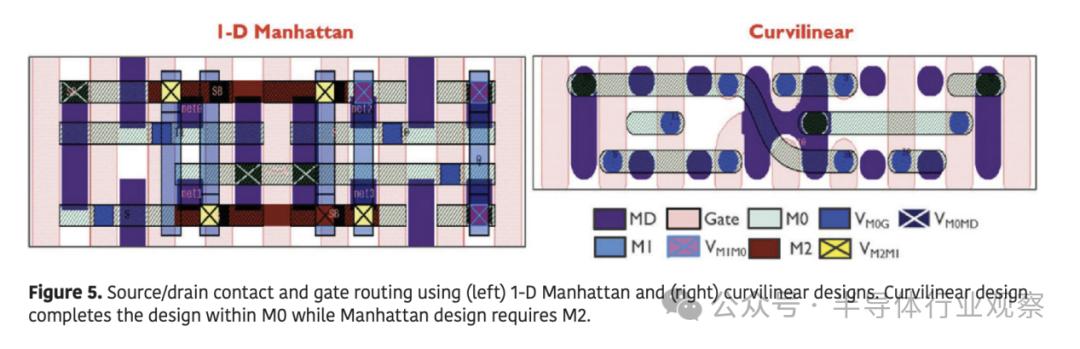

用例 2:源漏接触和格栅极再次通过曲线设计实现。

曲线设计的第二个应用领域是构成 CMOS 器件的 n 型和 p 晶体管源漏与栅极之间的线路接触。今天的一维曼哈顿设计,只能形成“南北”(north-south)电气连接角度。因此,连接 n 型和 p 增加额外的金属层和过孔层是晶体管源漏和栅极的唯一方法。这样可以使电流向上穿过过孔,沿着额外层中的走线金属流动,然后通过另一个过孔连接到另一个源漏接触。所以,在电气和成本方面都会造成损失。

但是,额外的金属层电连接(图5)可以通过使用曲线形状连接源极/漏极触点和网格来消除。通过降低M0线路资源的利用率,可以进一步缩小模块面积。将这一概念应用于行业代工厂14A节点逻辑标准单元,可以实现20%的面积缩小(相当于从5T单元设计转变为4T单元设计),同时抑制晶圆制造成本。

用例 3:曲线布局走线设计

与用例 1 和 2 相比,imec 感觉曲线几何在布局走线方面具有最大的潜力,其应用范围包括标准单元上方的所有金属走线层。与之前描述的用例不同,这种方法需要更多的工业投资,包括在整个设计空间内全面启用布局布局布局工具和提供寄生参数。 EDA 解决方案。imec 据估计,通过实现这一目标,曲线技术将在未来拓展思维技术节点方面发挥关键作用。

通过功率-性能-面积-成本-成本-成本,使用曲线设计的整体优势 (PPAC) 展示质量因素。现在,虽然具体目标不同,但是节点间转换目标的一个典型例子包括减少面积。 20%、性能提升 15% 和功耗降低 15%。如今,这些 PPA 优点是以晶圆制造成本为代价:行业试图将成本增长控制在节点间 20% 之内。根据 imec 估计,使用 14A 曼哈顿 1-D 通过在设计版图中加入曲线形状,设计可以进一步减少面积,同时提高功率/性能。这意味着行业可以在不缩小尺寸(即间隔)的情况下实现。 10A 的进展。更为重要的是,这些优点也带来了降低成本。在图案化领域,设计技术协同优化 (DTCO) 如何进一步加强节点间转换? PPAC 最好的优势示例。

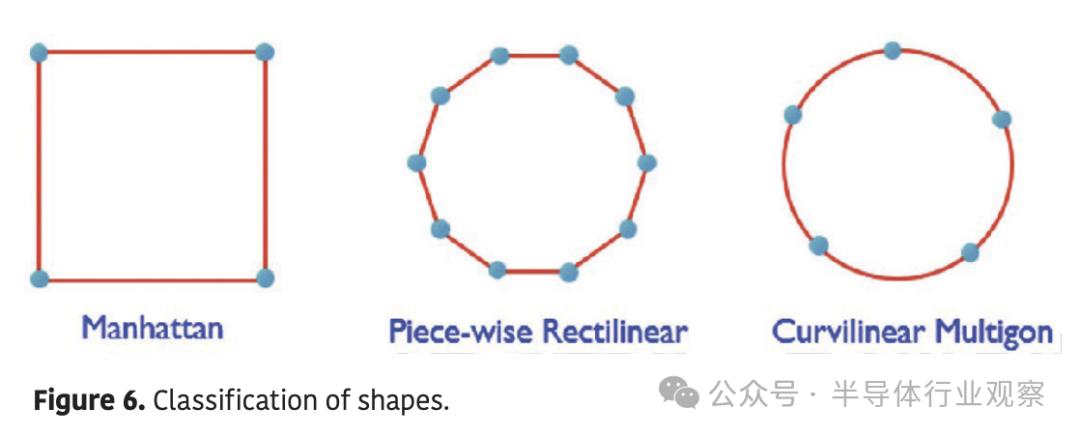

由于种种原因,建立曲线设计具有很大的挑战性。到目前为止,还没有找到一个解决方案来准确地表达曲线形状数据,同时控制整个生态系统的信息量。一种方案是使用分段直线数据表示法(一种由节点直线组成的几何结构)来类似于曲线形状(图) 6)。但是,使用这种表示法会大大增加信息量。由于商业用途,数据量过大是业界关心的问题, EDA 这种庞大的信息量很难处理,而且数据必须在整个制造生态系统中传输。

此外,还应建立特殊的设计规则,包括设备组件和布局图像特征。此外,我们还必须找到一种方法来检查设计的准确性——也就是所谓的设计规则检查 (DRC)。所有这些都必须能够通过商业使用 EDA 管理工具。

由于上述优点,曲线设计理念有望更有效地利用高数值孔径 EUV 光刻技术使其成为先进逻辑节点的补充技术选择。此外,这一创新理念有望扩大低值孔径 EUV 光刻技术,尤其是 193nm 浸没式光刻技术与图像传感器、超透镜或汽车芯片等其他应用领域密切相关,可以从降低制造成本中受益。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:imec,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com