重大突破!深圳诺奖实验室推出量产级RISC - V处理器IP

电子发烧友网报道 (文 / 章鹰)在全球处理器 IP 市场,除了 ARM、安谋科技、Synopsys、Candence、芯原等厂商外,如今又有了新的参与者。

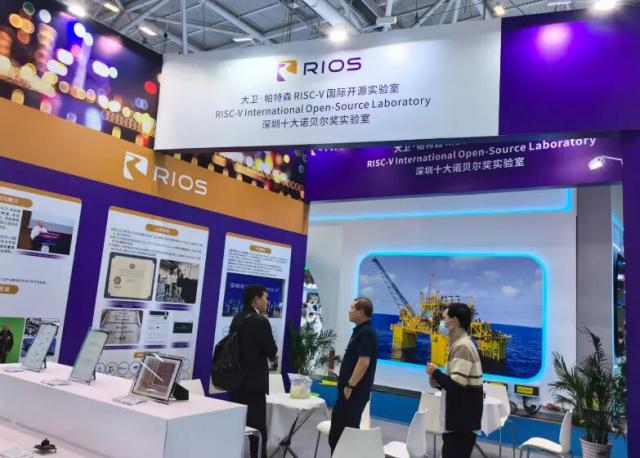

11 月 14 日至 16 日,在第 27 届中国国际高新技术成果交易会(简称“高交会”)上,由图灵奖得主大卫 · 帕特森教授团队建立的 RISC - V 国际开源实验室(RIOS)正式发布了其高性能开源 RISC - V 处理器 IP 核“OpenRio”。记者在 9 号馆看到了这家开源实验室的现场展示。

图:RISC - V 国际开源实验室(RIOS)展台 电子发烧友拍摄

作为深圳市资助的诺奖科学家实验室之一,RIOS 此次重磅开源其核心成果,这不仅是实验室发展的一个重要里程碑,更为国产操作系统生态提供了具有高度自主度的开放“芯”底座。

RISC - V 是一种开源指令集架构,它凭借开放、免费、可自由扩展的特性,打破了传统架构的壁垒。这种架构特别适合 AIoT、边缘计算等新兴场景,吸引了全球的创新力量,正逐渐成为继 x86 和 ARM 之后的第三大主流架构,对现有巨头构成了潜在挑战。

据介绍,OpenRio 是经过多轮验证、已实现量产的高可靠性 IP 核,它具备完善的国产操作系统框架支持能力,兼容主流 EDA 工具与工艺,可广泛应用于智能家居、工业控制、汽车电子等关键领域。

RIOS 实验室此次发布的 OpenRio,精准聚焦两大产业痛点:一是填补 ARM 在端侧产品线的空白,二是原生支持国产操作系统。它以“开源 + 近 ARMA520 级性能”的组合,为中小厂商与开发者提供了“零授权成本、高能效起点”的全新选择,降低了芯片的设计门槛,为 RISC - V 产业化注入了关键动力。

OpenRio 有助于解决国产操作系统生态长期面临的高性能、低成本核心供应问题,为产业链上下游企业开发创新终端产品提供支撑,将加速 RISC - V 技术在各行业的规模化应用与产业落地。

随着超大规模集成电路设计、制造技术的发展,集成电路设计进入了 SoC 时代,设计变得愈发复杂。为了加快产品上市时间,以 IP 复用、软硬件协同设计和超深亚微米 / 纳米级设计为技术支撑的 SoC 已成为当今超大规模集成电路的主流方向。当前国际上绝大部分 SoC 都是基于多种不同 IP 组合进行设计的,IP 在集成电路设计与开发工作中已不可或缺。

据悉,为了进一步推动产业协同,RIOS 实验室将同步构建开源 REPO 平台,致力于打造 CPUIP 开源底座,输出统一标准规范与参考实现,为产业提供持续、可信的技术供给。这一平台将逐步实现公共工具维护、产业链协同与生态人才培养等目标,助力形成“汇流成海”的生态效应,使大湾区成为全球嵌入式 RISC - V 的“创新策源地”。

更多热点文章阅读

点击关注 星标我们

源于工程师,服务工程师,华秋致力于提供电子产业链一站式服务,让硬件创新更简单。

喜欢就奖励一个“在看”吧!

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com