下一代EUV光刻,有多贵?

假设台积电是特朗普总统所说的“世界上最重要的公司”, EUV 毫无疑问,光刻设备是世界上最重要的设备。那是否意味着 SPIE 高级光刻与图案技术大会 (SPIE Advanced Lithography & Patterning) 成为世界上最重要的会议吗?不完全是这样,但至少是一种理解。 EUV 最新进展的好时机是先进逻辑领域。

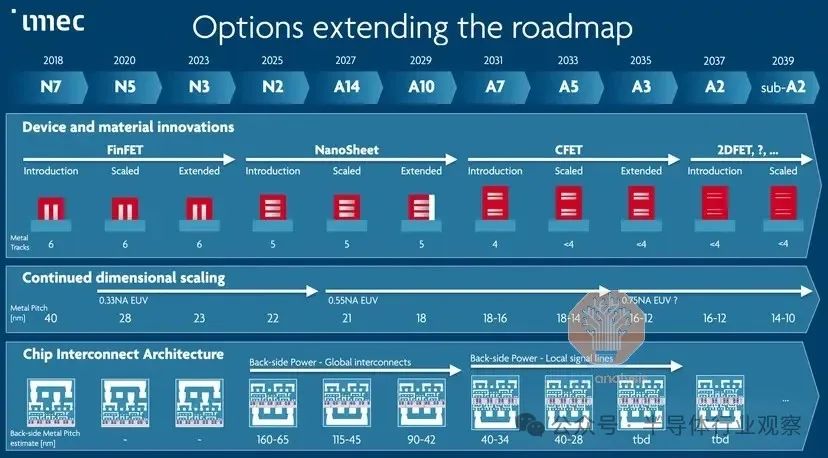

本报告将介绍今年会议的技术亮点及其市场影响。高数值孔径 (HDNA) 由于客户(英特尔)的设备正在大规模生产晶圆,这是本次会议的主要问题。比如图案成型(AMAT Sculpta 和 TEL Acrevia)互补图案化技术,如定向自组装,正在蓬勃发展。ASML 自己也已经进入了下一个主题:CFET 超高数值孔径的时代 (HyperNA)。

High NA 生产EUV的准备情况

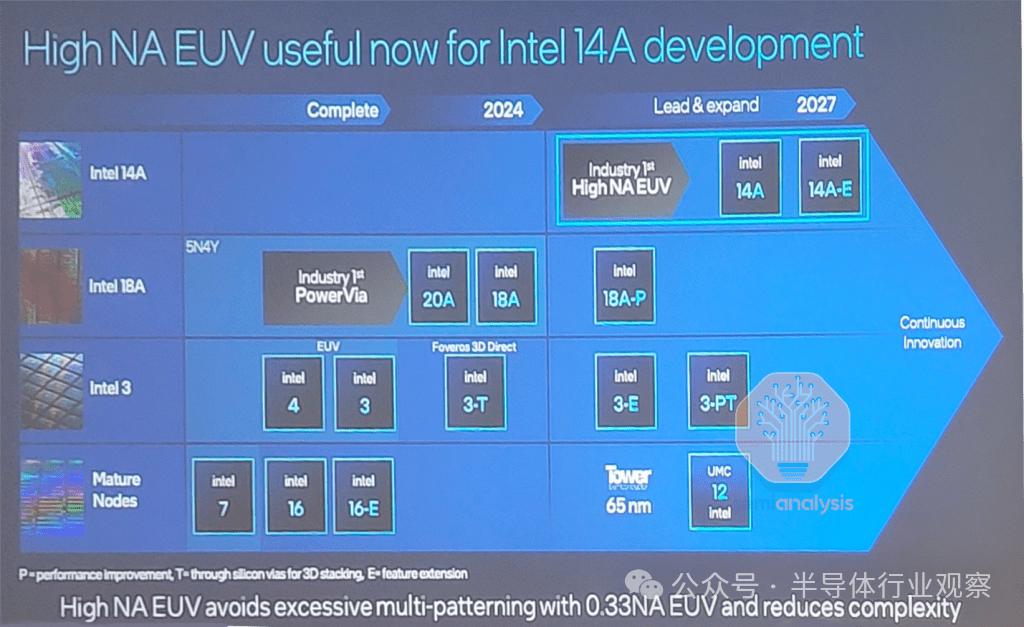

这次会议的亮点主题演讲是由英特尔的史蒂夫·卡森 (Steve Carson) 发布,内容是关于两个已经安装的高值孔径。 EUV 制造光刻机的准备工作。回顾过去,英特尔已经全力投入高数值孔径。 EUV 光刻机,一年多前安装了第一台出货光刻机。 EXE:5000,并且很快就接受了第二批光刻机,以便在竞争中抓住第一次机会,积累最初的经验。

显然,英特尔将High NA 尽管他们曾经说过,EUV是其推出14A节点产品战略的重要组成部分,但他们只需要Low就可以推出14A节点。 可以实现NA。目前已经完全安装的两台设备已经曝光了3万个晶圆,所以目前处于最佳位置,可以评价这款新型光刻机在生产环境下的可行性。它们的目标是以创纪录的速度推出一个新的High。 NA 开发试验线EUV系统,防止Low NA EUV带来的产能爬坡缓慢。

英特尔和 ASML 合作开发了许多新型扫描仪。(scanner)技术。扫描仪的常规制造工艺是在 ASML 根据客户和客户,费尔德霍芬工厂进行组装 ASML 约定的规格对装配好的设备进行检测。此后,设备将被拆卸并运送到客户的晶圆厂进行施工和重新组装。而且第一个高值孔径设备跳过了工厂集成和测试环节,直接从英特尔进行测试。

这种技术在第一台新型扫描仪中从未实现过,也是前所未有的——高数值孔径扫描仪与低数值孔径扫描仪有着显著的区别。ASML 与英特尔在这个过程中密切合作,因为很多关于如何启动和提高设备可靠性的程序和方法都是第一次接触。

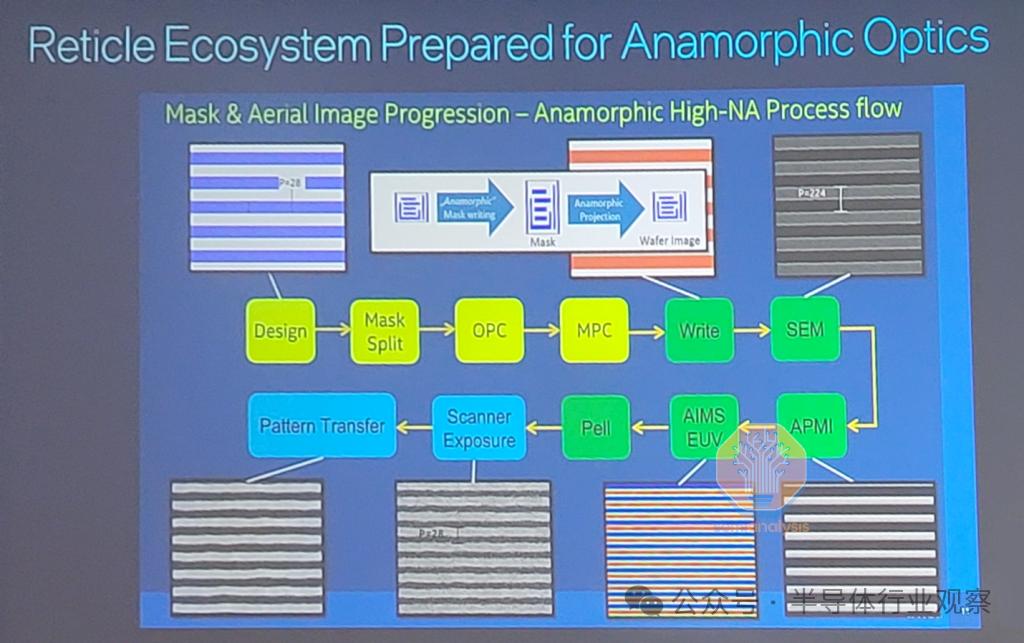

然而,仅仅依靠一个功能齐全的扫描仪,它只是一个高数值孔径问题的冰山一角。这条试生产线还需要技术、面罩(掩模版)和光学校准。 (OPC) 只有等待技术,才能紧迫。 14A 时间表已经准备好了。这特别困难,因为四个要素相互依存,这意味着开发必须按顺序进行。英特尔被迫在这方面进行创新,并尽可能实现并行化。

工艺部分包括光刻胶,英特尔共同使用LowNA。 NXE系统和伯克利的微场曝光工具用于表征和筛选High高NA的光刻胶。现阶段一般决定了将图案从光刻胶转移到底层材料堆放的蚀刻过程。

OPC 它是一个复杂的软件套件,用来将ic设计转换成光刻掩模版的复杂形状。一般,OPC 该模型将使用实际扫描仪,POR(process of record)为了打印真实的晶圆,光刻胶和蚀刻剂进行校准。设备模板覆盖 OPC 模型(通常称为“模型”keyword)需要了解许多工艺细节。它们含有蚀刻偏置表,因此,必须首先开发和表征蚀刻工艺。新型扫描仪独特的,针对特定照明光瞳的通距偏置,也对新型光刻胶进行了表征。

但是当时HighNA扫描仪还没有出现。所以,英特尔开发了一种不需要真实晶圆数据就可以校正OPC模型的新方法。它们采用模拟和低NA曝光相结合的方法,并利用这些曝光信息进行外推,最终调整High。 NA OPC模型。由于OPC模型在没有晶圆数据校正的情况下精度会很差,所以通常不会采用这种方法,但是英特尔证实了这是合理的。

OPC 由于高数值孔径光罩具有较小的特征尺寸和新的变形设置,因此模型对于制作高数值孔径光罩尤为重要,而低数值孔径光罩则不然。因为 OPC 为了满足扫描仪的认证要求,模型不再是关键路径,光罩可以及时生产,并且几乎立即投入试产线。传统上,这个过程需要几个月的时间才能被扫描仪验收,而英特尔和 ASML 把它缩短到几乎为零。对一种全新的扫描技术而言,如此短的启动时间是前所未有的。

高值孔径显像结果

在安装好扫描仪并准备好光罩之后,英特尔就可以对该设备进行功能测试。远远超过新扫描仪系统的基本指标,如灯源功率和可靠性。新型EUV系统首次超过了初始目标值,灯源功率达到了目标值的110%。相比之下,NXE:第一次出货时,3300开发系统仅为目标值的15%,而NXE:3400B生产系统仅为目标值的50%。事实上,ASML已经领先于它的灯源路线图。在同一开发阶段,可靠性达到85%,也明显优于所有以前的系统。

套刻性能(Overlay performance)令人印象深刻的-0.6纳米套刻精度和低值孔径(NA)工具对准。这类跨多种工具的优异性能通常被认为是理所当然的,但却是 ASML 特别之处的一部分。在不将关键层限制在同一个工具甚至同一个晶圆卡盘上的情况下,它使芯片制造商能够灵活地混合搭配各种工具,并获得良好的效果。竞争者在这方面落后于数纳米。

这个overlay的结果可以使英特尔和 ASML 宣布,高数值孔径 (NA) 对缝合区域(stitched fields)没有任何影响。由于高数值孔径的光电设备会限制区域大小,所以这一直是个大问题, GPU 这种大芯片需要缝合。尽管他们已经声明,但是没有晶圆厂的客户是否会接受缝合芯片仍然是一个悬而未决的问题。至少在缝合区域可能存在设计规则的限制。

关于光刻胶厚度的共识是,高数值孔径光刻技术需要更薄的薄膜镀层,这将影响所需的光学焦深度。英特尔可以评估这个影响可制造性的关键工艺参数。新型高数值孔径设备的焦点控制性能优于低数值孔径 NXE 系统,并且符合目标规格。

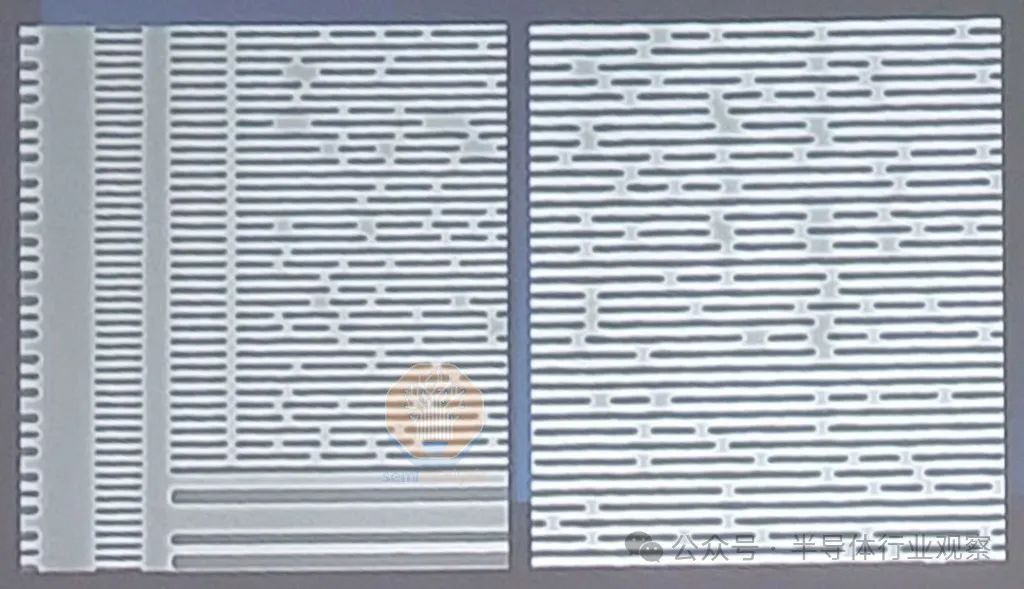

除核心光刻性能外,英特尔还分享了金属层及接触孔层的初始设备数据。这两层都是14A光刻技术的关键层,High NA EUV技术可以决定良率。对金属层而言,这次比较使用了High。 NA曝光取代现有的金属化方案,该方案包括三次Low NA曝光,总共有40多个工艺步骤。

值得注意的是,low 选择间隔分割的NA工艺选择(pitch splitting)双重曝光与自对准(SADP)突破LowNA的技术 一次曝光EUV的限制。英特尔称之为自对准光刻蚀刻刻蚀刻(SALELE:self-aligned litho-etch litho-etch)。由于依赖于原子层沉积,SADP需要许多工艺步骤。(ALD)将金属间隔与一系列蚀刻工艺分割成所需的几何形状。另外,EUV两次曝光用于切割掩模版本,用于修整间隔分割引起的线条,并对较大间隔的金属特征进行图案化。High NA工艺用一次曝光和更少的工艺步骤取代了所有这些步骤。

High SEM图像在NA一次曝光,图案转移后,用于1x金属走线。

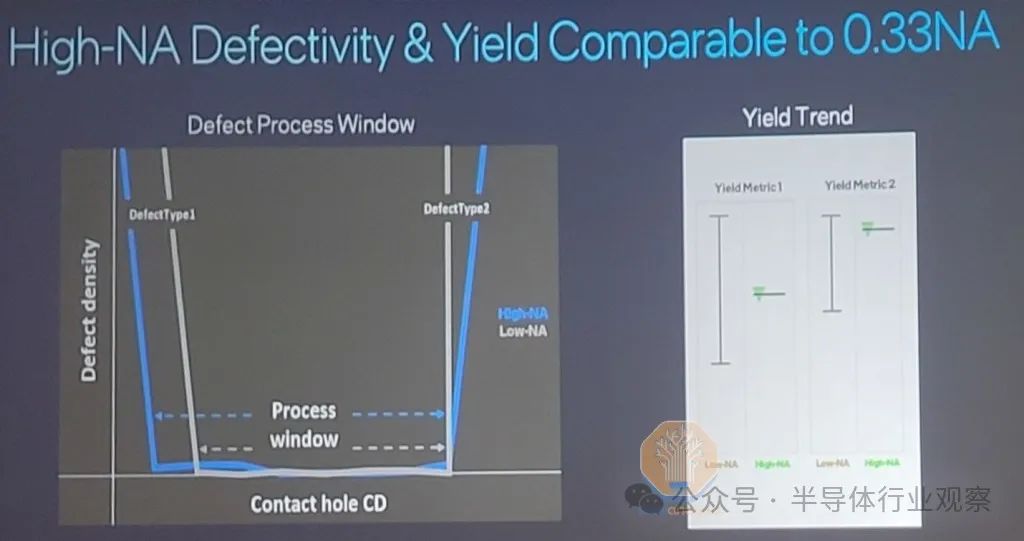

对于触碰孔 (CH:contact-hole) 层次,英特尔共享良率数据,显示高数值孔径 (NA) 技术的良率和现有的低值孔径 (LELE:low-NA multi-patterning) 多种曝光工艺的良率相似。值得注意的是,早期用于测量层健康状况的掩模版在提供理想结果方面表现不佳。通常需要多次迭代 OPC 只有通过转动掩模版才能获得即时良率信号。所以,现阶段,高数值孔径工艺与成熟工艺的良率相当,令人印象深刻。

她们没有透露Low NA掩模步骤的数量没有透露工艺步骤的总数。我们假设,在最终蚀刻转移和金属化之前,我们会把Low重复两次。 NA模具存储在硬模具中。

最后,英特尔呼吁大家积极参与新的掩模基础设施建设,并大胆宣布其两个高数值孔径 EUV 现在系统已经“投入生产”了。“投入生产”是指在验证过程中运行测试晶圆,而不是运行商业产品的高数值孔径光刻机。

这里使用的已验证过程很可能是 18A,由于处于开发的最后阶段,与潜在客户进行模板流通,工艺步骤基本确定。这是为了用高数值孔径代替一个或多个关键层。 (NA) 这个实验提供了一个方便的标准。并且现在已经完全表现出来了 18A 低数值孔径 (NA) 的 POR 进行比较,可以为 14A 研究与开发提供了宝贵的反馈。

这个概念也用来检测很多新技术,保证在量产前验证。使用7nmlow NA 以EUV为例,它被用来在合理的成本之前获得良率经验。当时初始灯源的功率太低,无法将EUV与DUV的四重图案技术进行竞争。

High NA光刻的费用

ASML 最新的高数值孔径系统 EXE:5000 重约惊人的 150 公吨,成本接近 4 十亿美元。它的价格几乎是低值孔径系统的两倍,这直接导致了更高的运行成本,最终导致晶圆成本的增加。

正如我们正在谈论High一样 NA与low NA多次曝光报告中讨论的设备选择取决于成本。虽然减少复杂性是一件好事,但并不是所有的前提下都更便宜。这是英特尔演讲中忽略的一点。它比低 NA LELE还是SALELE更便宜?

因为它们正在“生产”中,并且把支系High 他们必须知道答案,直接比较NA运行路径和这些替代方案。英特尔、imec和IBM都在推动High在14A节点的选择。 NA;但是,过早投入大量的扫描仪来运行生产线(投入数十亿美元)可能和过晚投入新的支持技术一样有害。

SPIE 策划者习惯于在周四下午安排最重要的演讲,其中一场演讲来自 IBM 的 Luciana Meli 主持人,她发布了唯一一个关于主持人的故事。 150 吨重大象的演讲——High NA 有成本效率吗?

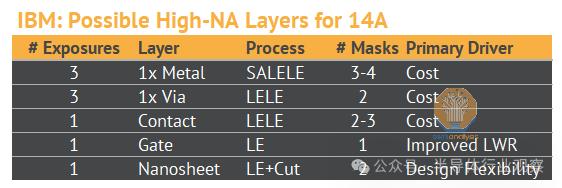

IBM 基于模拟和它们的存在 Veldhoven High NA EUV 实验工作,提出了几个关键的发现。第一,他们决定使用一次High。 NA 曝光取代Low数次 NA 曝光,最有可能带来好处的 14A 层:

其成本分析集中在成本分析上 SALELE 其实,因为它有最高的节约成本的潜力,可以使用一次High。 NA 曝光取代Low3-4次。 NA 曝出。这里的详细信息弥补了英特尔谈话中遗漏的一些关键问题。首先,SALELE 里面的工艺步骤大约是High。 NA 一次曝光所需步骤的两倍。回想起来,英特尔说,对于他们的三掩模工艺,SALELE 大概有 40 工艺步骤;所以,High NA 在模块中,流程数仍然非常重要。对于成本,IBM 宣称四掩模 SALELE 过程比High一次要好 NA 曝光成本高 1.7 到 2.1 倍。这一结果并不令人惊讶,但却是一个很好的成本数据点——估计High NA 一次曝光将是Low的三倍或四倍。 NA 曝光更便宜。

然而,IBM 还有助于我们验证我们关于High的问题。 NA 与low NA 双曝光模型,说明Low NA 方案比较便宜。它们的数据显示,一次High NA 曝光的费用大约是一次Low。 NA 曝出的 2.5 倍。除非有效地说明三个Low, NA 模板模板缩减为High NA 隐藏模板,否则High NA 一次曝光的所有成本优势也不会显现。

IBM 演示的另一个有趣的发现是,High NA 一次性曝光的金属工艺可能不能满足金属点对点。 (tip-to-tip) 设计目标。值得注意的是,low NA SALELE 该技术在这方面表现良好,采用专用切割掩模定义点对点。 (tip-to-tip) 的特点。IBM 推荐使用定向蚀刻技术(例如应用材料公司) Sculpta 为了弥补这个缺陷,工具)将在下面详细介绍图案成形技术。

高数值孔径 6 x 12 英尺掩膜

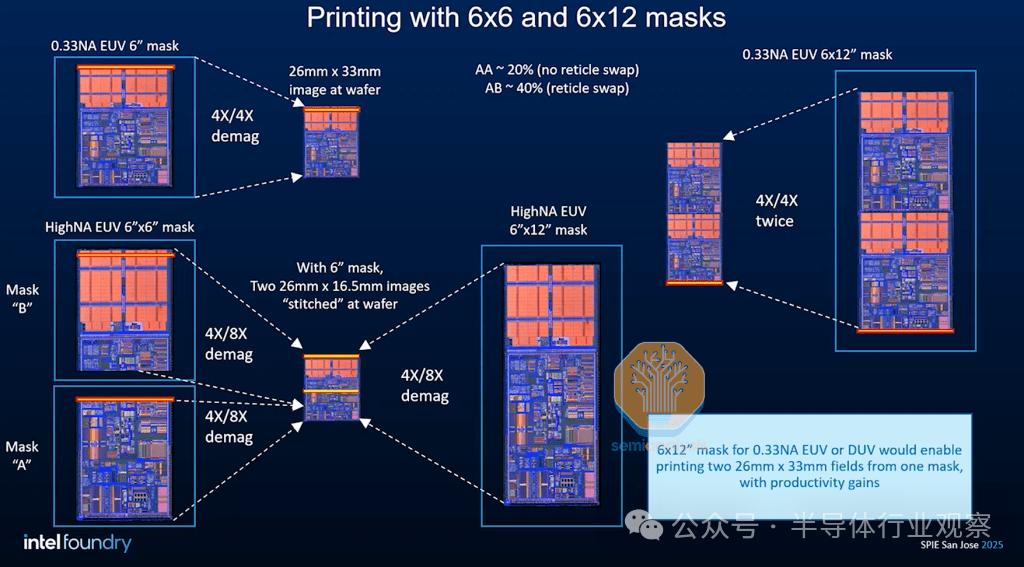

英特尔全体会议演讲的最后一个ppt呼吁大家积极推广大型高值孔径模板。他们一直在强调这一点,理由充分:一个6。 x 12英寸的掩模版,是行业标准的6英寸。 x 6英尺模板的两倍,将使扫描仪的生产效率提高23%至50%。

6 x 12英尺掩模可以增加吞吐量,消除高数值孔径场拼接问题

它支持整个曝光,消除拼接问题,增加吞吐量。假设扫描仪的成本合理增加,这将显著影响关键层的经济效益,使其显著有利于高数值孔径。

为了提高生产效率,降低成本,英特尔呼吁客户选择更大尺寸的高值孔径模板,

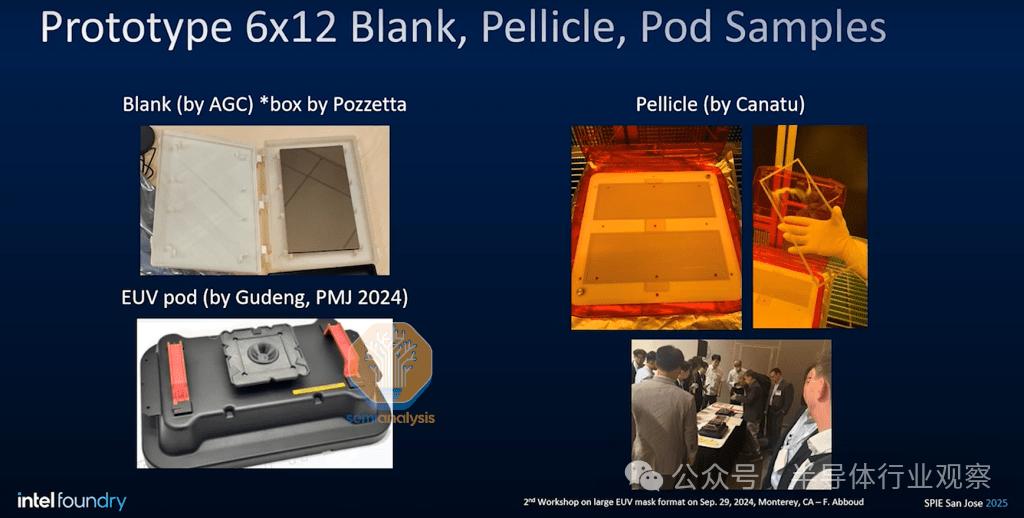

尽管英特尔和其他公司表示,在掩模生态系统中,大型掩模并没有受到重大挑战,但是真正的转折点实际上取决于 ASML。虽然CEO Christophe Fouquet 去年在 SPIE EUV 会议上的所有会议都对大型模板保持积极的态度,但当时技术并没有纳入路线图,公司也没有正式宣布技术可以或即将开发。今年,ASML 在整个会议上,更进一步表明更多的“生态系统在进步”和“影响研究正在进行”,这项技术可能会在“未来十年初”的某个时候推出。

ASML承认生产大型模板的可能性

它不是一个小小的改变。自20世纪80年代投射光刻技术问世以来, x 6英寸的掩模尺寸一直是常规尺寸。所有工装:毛坯制造、光刻胶涂装、电子束写入、模具清洗、晶圆厂处理等,必须根据新的模具尺寸进行重建。相当于把晶圆尺寸从200mm提高到300mm(10年前试图升级到450mm失败)。这一时间轴肯定超过了14A节点技术的改进范围。

对于 ASML 而言,6×12 英尺模板及其核心模板 EUV 制度战略相反。ASML 希望将 NXE、EXE 以及未来的极高数值孔径 (Hyper-NA) 为了简化生产流程,系统整合到一个通用平台上,其中一个改进就是光罩平台和处理系统。大型模板必须对这些模块进行重大改变,并且可能会破坏实用性。

EUV光刻机将在未来迁移到通用平台

也不符合大型掩模版本 ASML 经济效益。如果要在两台常规高值孔径掩模光刻机和一台大型掩模光刻机之间做出决定,那么两台完整的光刻机可能会出售。 ASML 带来 2 亿到 3 一亿美元的额外收入。对于客户来说,开发大型掩模光刻机非常有利。

High NA EUV:插入14A还是10A?

采用14A工艺,High NA只在少数金属层中具有成本优势,在英特尔工艺中可以替代三层光罩。需要注意的是,台积电在A14工艺中不一定使用三重EUV进行曝光,这是英特尔独有的。英特尔指出,在其他层中,它提供了设计灵活性和工艺简化——这些优点与成本无关。

仅仅为了降低三层的成本,是否值得提前引进新技术?虽然成本确实降低了,但是与大约100层的整体芯片技术相比,它所占的比例非常小。即使没有High,英特尔甚至明确表示。 NA,14A工艺也是可行的,尤其是在顾客有需求的情况下。但是现在大多数迹象表明,High是英特尔将到14A技术的关键级别。 NA。这家公司内部的惯性可能太强了,现在很难改变方向。如果6 x 12英尺覆盖模板可以充分准备隐藏的10A技术,从而带来非常有利的经济效益,因此英特尔可能会从最初的选择中受益。现在,它在High NA方面的学习和专业知识远远领先于竞争对手。

光刻胶,金属氧化物

近几年来,金属氧化物光刻胶 (MOR:Metal-oxide resist ) 永远是“下一个” EUV 光刻胶平台。光刻胶与成熟的有机化学放大 (CAR:chemically amplified resists ) 相比,MOR 光刻胶提供了更好的分辨率-线距-灵敏度 (RLS:Resolution-LER-Sensitivity) 性能。因为 EUV 由于光子的限制,灵敏度和线距粗糙度(或 CD variance)至关重要。在 13.5nm 在波长下,光源发射的光子较少,但与 DUV 波长,它的功率要高得多。细微的剂量灵敏度改善可能会对吞吐量产生重大影响,从而影响运营成本。

但是,光刻胶平台的变革和任何新技术一样,都需要很大的动力才能引起整个行业的选择。对当前节点而言,其优势不足以引发变革。

RLS 光刻胶性能衡量的概念

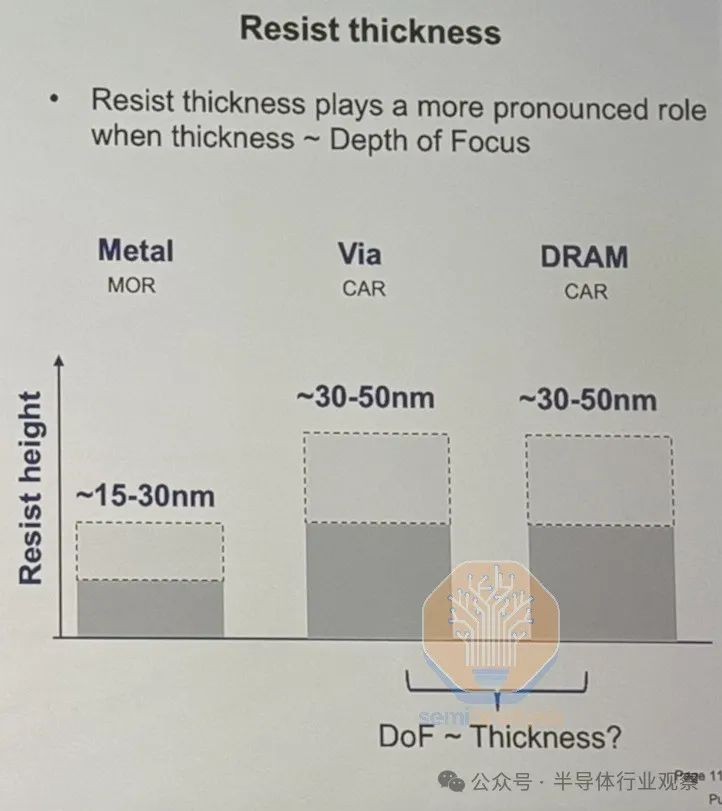

伴随着高数值孔径 (NA) 的引入,MOR 时代似乎终于到来了。焦深也是一个关键的驱动因素,因为它会伴随着数值孔径。 (NA) 平方而降;这意味着高数值孔径扫描仪的焦深特别小。景深 (DoF) 同时也会受到照明光瞳的影响,为了产生最佳图像,必须对特定图案进行优化。遗憾的是,对于越来越小的图案,最好的光瞳通常会降低景深。镜面数值孔径与照明光瞳的共同作用都会降低焦深,从而达到一个临界点,到时候必然会产生非常薄的光刻膜。

光刻胶的厚度必须低于焦深,这样图像才能集中在整个光刻胶的高度,否则光刻胶中形成的图案质量会很差。这个区域就是薄MOR光刻胶比薄CAR光刻胶好。传统的CAR光刻胶平台利用有机丙烯酸聚合物主链(碳-碳链)作为阻挡蚀刻的基础,同时将图案转移到氮化硅等硬掩模板。(SiN)。薄有机聚合物薄膜不具有足够的耐蚀性,难以承受图案转移;但是,金属氧化物光刻胶具有更好的蚀刻选择性,可将图案转移到大多数硬质模膜中。所以MOR光刻胶的光学和蚀刻性能优于CAR光刻胶。

光刻胶的厚度随着焦深的减少而成为挑战

以埋孔为例,埋孔是一种图案密切的孔,金属层之间的互连是通过添加金属来形成的。它的交接点似乎在 30 上下纳米间隔。从现在起约 2 一个节点之后,在 A10 过程中,埋孔可能会缩小到这个间隔。这符合我们什么时候引入高值孔径? (NA) 有经济预期。也就是说,对于少数关键层(如金属和埋孔), MOR 跟随高数值孔径 (NA) 也许是合理的。大多数数据,包括今年的高数值孔径曝光。 SPIE 所有的论文都使用了 MOR 而不是 CAR。

更多的研究将决定光刻胶未来的战争。MOR 还有待确定是采用湿法还是干式涂布和显影工艺。TEL 其湿旋涂和湿法显影工艺都是目前的标准,其工艺流程在这方面占据主导地位, Track 完成设备。Lam 然后试图通过干式光刻胶沉积和蚀刻显影技术在关键层占据市场份额,这两种技术都是在其设备上完成的,不同于传统的光刻机。

这些都是值得关注的地方。

Hyper NA,未来目标

展望未来,以及下一代EUV光刻机——Hyper NA EUV光刻机。

当时的ASML2023年 首席技术官 Martin van den Brink 曾在公司年报中写道:“NA 高于 0.7 超高值孔径无疑是一个机会,而且从 2030 大约一年后开始变得更加明显。” 他说:“这可能是最适合逻辑芯片的,而且这需要比逻辑芯片更多 [高数值孔径 EUV] 双曝光更经济-但也可能是为了 DRAM 带来机遇。对于我们来说,关键在于极高的数值孔径正在推动我们的整体。 EUV 为了降低成本和缩短交付周期,能力平台的改进。”

ASML 目前的 EUV 该设备由低值孔径组成 (NA) 模型组成,其光电器件数值孔径 (NA) 为 0.33,可实现 13.5 临界尺寸纳米 (CD)。这足以通过一次曝光图案来实现。 26 最小金属间距与纳米 25-30 类似的纳米互连间隔。足够满足这些尺寸 4 纳米/5 需要纳米生产节点。但是,行业需求 3 达到纳米间距 21-24 纳米,所以台积电 N3B 目的是采用低数值孔径生产工艺 EUV 双图案技术可以打印出尽可能小的间距。这一方法被认为是非常昂贵的。

具有 0.55 NA 下一代High是光电器件。 NA EUV 系统将实现 8nm 的 CD,足以打印合同 16nm 最小的金属间隔,这对 3nm 接下来的节点非常有用,并且估计即使对 1nm 而且足够好,至少根据 Imec设想的数字。

然而,金属间隔将进一步缩小到1纳米以下,因此行业将需要比ASML高数值孔径设备更专业的设备。这促使我们开发了超数值孔径,具有更高的数值孔径投射光学系统(Hyper-NA)设备。Martin van den 确认Brink ,它们正在研究超数值孔径技术的可行性。然而,目前还没有做出最终决定。

在光刻工具的设计上,增加投射光学系统的数值孔径是一个昂贵的过程。具体而言,它包括机器的物理尺寸,开发许多新组件的需要,以及成本上升的影响。ASML 最近的披露,低 NA EUV Twinscan NXE 这台机器的费用是 1.83 一亿美元或更高,具体取决于配置, High NA EUV Twinscan EXE 这个工具的价格是 3.8 一亿美元或更高,具体取决于配置。Hyper NA 成本会更高,所以 ASML 必须回答两个问题:它是否能在技术上实现,以及芯片制造商是否具有经济可行性,这是一个领先的想法。

只剩下三家领先的芯片制造商:英特尔、三星和台积电。总部位于日本 Rapidus 还没有发展成可行的竞争者。所以,尽管hyper需要 NA EUV 光刻技术,但是它必须有合理的价格。

“Hyper-NA 这取决于我们能够降低成本的水平,”Martin van den Brink曾经说过 。他说:“我多次走遍世界,与客户讨论。 Hyper-NA 必要和可取。最近几个月,我逐渐明白,顾客希望进一步降低分辨率,所以, Hyper-NA 逻辑和内存芯片的大规模生产是可能的。在接下来的十年里,这将会实现。但是最终取决于成本。”Martin van den 在2023年的一次采访中,Brink提到。

参考链接

https://semianalysis.com2025/04/14/spie2025/2025/

本文来自微信微信官方账号“半导体行业观察”,作者:semianalysis,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com