HBS存储技术:堆叠DRAM与NAND,基于VFO封装工艺的创新突破

电子发烧友网综合报道,据韩媒消息,存储行业巨头SK海力士正集中精力攻克一项全新的性能瓶颈技术——高带宽存储HBS。

SK海力士研发的HBS技术采用了独特的芯片堆叠方案。按照规划,该技术会借助名为垂直导线扇出(VFO)的封装工艺,实现最多16层DRAM与NAND芯片的垂直堆叠。这种高密度的堆叠方式能够极大地提升数据处理速度,为移动设备的AI运算提供坚实的存储支持。

此前报道显示,移动HBM通过堆叠和连接LPDDR DRAM来增加内存带宽,同样运用了VFO技术。SK海力士正在开发的VFO技术选用铜线而非铜柱。DRAM以阶梯式方式堆叠,接着将环氧树脂注入空白处使其硬化,以此实现移动DRAM芯片的堆叠,并通过垂直柱状线/重新分布层连接到基板。

SK海力士的VFO技术融合了FOWLP(晶圆级封装)和DRAM堆叠两项技术。VFO技术通过垂直连接,显著缩短了电信号在多层DRAM间的传输路径,将线路长度缩短至传统内存的1/4以下,能效提高了4.9%。虽然这种方式会使散热量增加1.4%,但封装厚度减少了27%。

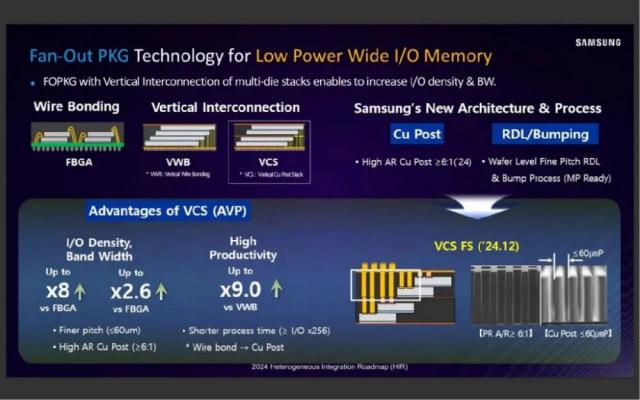

在移动HBM领域,三星也在积极开发VCS技术。该技术把DRAM芯片以台阶形状堆叠起来,用环氧材料使其硬化,再在其上钻孔并用铜填充。三星表示,VCS先进封装技术相较于传统引线键合,I/O密度和带宽分别提升了8倍和2.6倍;相比VWB垂直引线键合,VCS技术生产效率提升了9倍。

与移动内存LPDDR5X相比,新款移动HBM LPW DRAM的I/O速度预计将提高166%,同时功耗降低54%。预计搭载LPW DRAM内存的首款移动产品将在2028年上市。

就HBS存储而言,VFO封装摒弃了传统的弯曲导线连接方式,采用直线直接连接堆叠的DRAM和NAND芯片。这一改进不仅大幅缩短了布线距离,还能有效减少信号传输过程中的损耗与延迟,同时支持更多的I/O通道,从多个方面推动整体数据处理性能的显著提升。

此外,HBS无需采用HBM所依赖的硅通孔TSV工艺,不仅降低了制造成本,还能有效提高产品良率。未来HBS将采用与手机芯片组协同封装的模式,再一同安装到设备主板上,实现硬件层面的高效适配。

目前,SK海力士尚未公布HBS技术的具体量产时间表,但相关研发进展已引起行业的广泛关注。HBS技术的成功研发与量产,将为智能手机、平板电脑等设备带来更强大的本地AI处理能力,推动AI应用从云端向终端普及。市场预计,随着技术的不断成熟与完善,HBS存储有望在未来2 - 3年内实现商业化应用,成为移动终端存储的新一代标杆产品。

更多热点文章阅读

点击关注 星标我们

将我们设为星标,不错过每一次更新!

喜欢就奖励一个"在看"吧!

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com