3D NAND技术的演进之路

NAND闪存自20世纪80年代末进入存储器市场,彻底改变了数据存储和检索方式。这种专为高密度数据存储设计的非易失性存储器,广泛应用于电子市场各领域,如智能手机、数据中心,以及大多数可移动和便携式存储设备,像SD卡和U盘。近年来,3D NAND在人工智能发展中发挥了重要作用,为训练人工智能模型的大量数据提供了高效存储方案。

随着数据存储需求的爆发式增长,芯片公司努力提高NAND闪存的存储单元密度,降低每比特成本。十多年前,半导体行业从二维NAND过渡到三维NAND,以突破传统存储器尺寸缩减的限制。近年来,各公司通过增加芯片存储单元层数和每个单元的存储比特数来提升存储密度。

其中一项重要进展是从浮栅晶体管向电荷陷阱单元的转变。浮栅技术将电荷存储在导体中,而电荷陷阱单元将电荷存储在绝缘体中,降低了存储单元间的静电耦合,提高了读写性能。而且,电荷陷阱单元制造尺寸更小,为更高存储密度奠定了基础。

然而,随着3D NAND技术逼近物理极限,半导体行业转向多种新技术,以更紧密排列存储单元。imec开发的气隙集成和电荷陷阱层分离等创新技术,实现了垂直方向扩展,且不影响存储器性能和可靠性。

电荷陷阱单元内部:3D NAND的基本构建模块

半导体行业计划未来将全环栅(GAA)或纳米片晶体管用于逻辑芯片,而GAA架构已在3D NAND闪存领域广泛应用,是高密度数据存储的主力。在3D架构中,存储单元堆叠成垂直链,通过水平字线寻址。

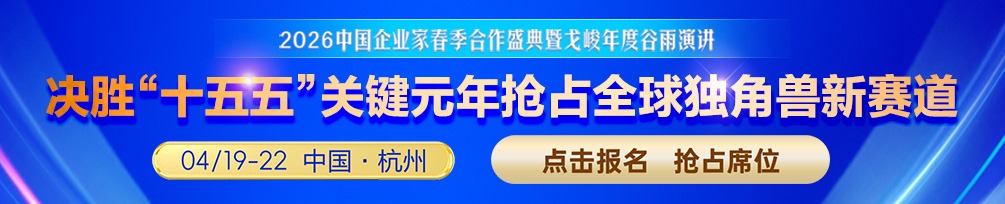

多数情况下,电荷陷阱单元作为3D NAND的存储器件。它类似MOSFET,在晶体管栅极氧化层内嵌入一层氮化硅(SiN),使栅极氧化层成为氧化物 - 氮化物 - 氧化物(ONO)堆叠的半导体材料层,各层分别用作阻挡氧化层、捕获氮化物层和隧道氧化层(图1)。

1.该图显示了一个3D NAND GAA架构,它具有一串垂直的电荷陷阱单元,该单元具有氧化物 - 氮化物 - 氧化物 (ONO) 栅极介质和有限数量的字线 (WL)。

当栅极施加正偏置电压时,沟道区电子隧穿氧化硅层并被捕获在氮化硅层中,提高晶体管阈值电压。通过在源极和漏极间施加电压测量存储单元状态,有电流表示“1”状态,无电流表示“0”状态。

电荷陷阱单元采用GAA垂直沟道方法实现。制造时先交替堆叠导体(硅,用作字线)和绝缘层(氧化硅,分隔字线),再用先进干法刻蚀工具钻孔形成圆柱形孔,最后在孔侧壁交替沉积氧化硅和氮化硅层,多晶硅晶体管沟道位于中心,这种结构被称为“通心粉沟道”。

下一代3D NAND:单元堆叠和单元缩放

未来几年,存储器行业将把基于GAA的3D NAND闪存路线图推向极限。

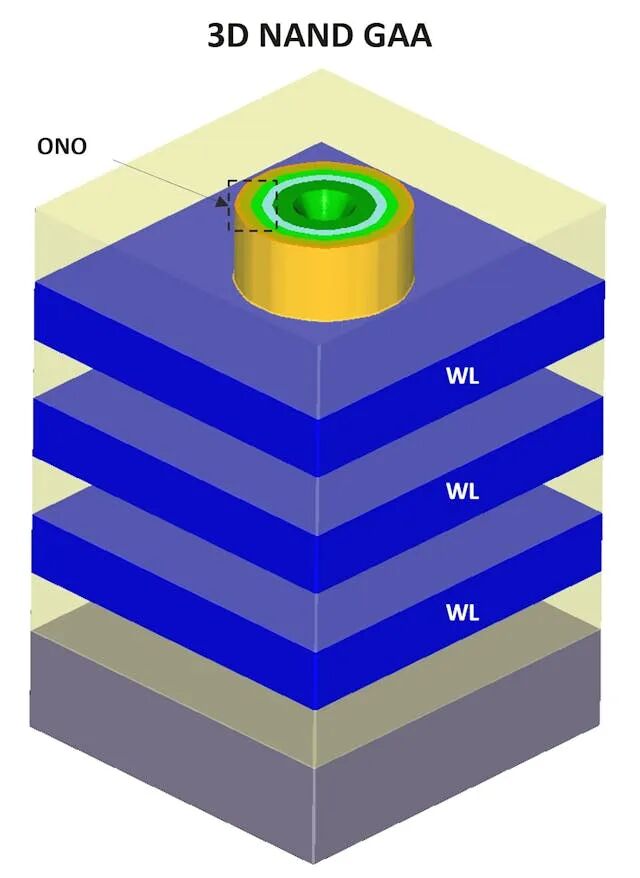

如今,主流厂商推出超过300层氧化物/字线堆叠的3D NAND闪存芯片(图2)。预计到2030年,层数将达1000层,存储容量约100 Gbit/mm²。但挑战在于在30微米厚的堆叠层中保持字线直径一致,这增加了工艺复杂性和成本,对高堆叠沉积和高深宽比刻蚀工艺要求更高。

2. 这张3D NAND闪存图突出了相邻字线之间的z间距。

为配合堆叠更多层数,半导体公司投资开发多种工具提高存储密度,如增加每个单元的比特数、减小GAA单元的xy间距,还采取措施提高存储阵列面积效率。

层叠技术也是提升存储容量的方法,即将闪存器件堆叠增加总层数。在3D NAND闪存中,存储单元串联成链,通过交替堆叠绝缘层和导体层并钻孔实现。单元堆叠可重复多次,企业可组装多层存储单元再堆叠成更高层数的芯片,但蚀刻深孔并均匀填充是主要挑战。

此外,一些公司将底层逻辑从NAND阵列分离,以CMOS键合阵列(CbA)配置重新集成到NAND阵列上。CbA是CMOS下置阵列(CuA)的发展阶段,未来各公司还考虑将多个存储阵列粘合到单个CMOS晶圆上。

为控制成本,imec等企业探索垂直或“z间距”缩放技术,减小氧化层和字线层厚度,以可控成本堆叠更多存储层。

3D NAND闪存Z间距缩放的优缺点

缩小存储层间距对降低下一代3D NAND成本至关重要。z轴间距缩放旨在减小堆叠结构中字线层和氧化硅层厚度,增加存储层数和单元数量,从而降低成本。

然而,不优化的z轴间距缩放会影响存储单元电性能,导致阈值电压降低、亚阈值摆幅增大、数据保持能力下降,还会增加编程和擦除电压,增加功耗、降低速度,可能导致相邻单元间栅极介质击穿。

这些效应源于细胞间干扰和横向电荷迁移。当字线层厚度减小,电荷陷阱晶体管栅极长度缩短,栅极对沟道控制能力减弱,促进单元间静电耦合。同时,存储单元垂直缩小会导致横向电荷迁移,影响数据保持。电荷可沿xy和z方向从存储单元泄漏,随着单元垂直尺寸缩小和间距减小,横向电荷迁移更显著。

接下来将讨论解决这些缺点的技术,以实现未来3D NAND闪存的z间距缩放。

字线间:利用气隙减少Cell干扰

在相邻字线间集成气隙是解决单元间干扰的潜在方案。气隙介电常数低于栅极间介质,可降低存储单元间的静电耦合。该技术已用于平面二维NAND闪存架构,但集成到高硅氧化物/字线堆叠结构更具挑战。

imec在2025年IEEE国际存储器研讨会(IMW)上提出独特集成方案,可精确控制字线间气隙位置。

在3D NAND存储器中,氧化硅存在于存储单元内部和单元之间。由于制造工艺,栅极介质从一个单元延伸到另一个单元,并与栅极间介质相交,imec认为此为放置气隙的理想位置,但去除单元间的电荷陷阱SiN层仍是挑战。

imec找到无需切割SiN即可集成气隙的方法,通过在沉积ONO堆叠层前对栅间氧化硅凹陷,从存储孔区域内部引入气隙,气隙与字线自对准,且具有潜在可扩展性。

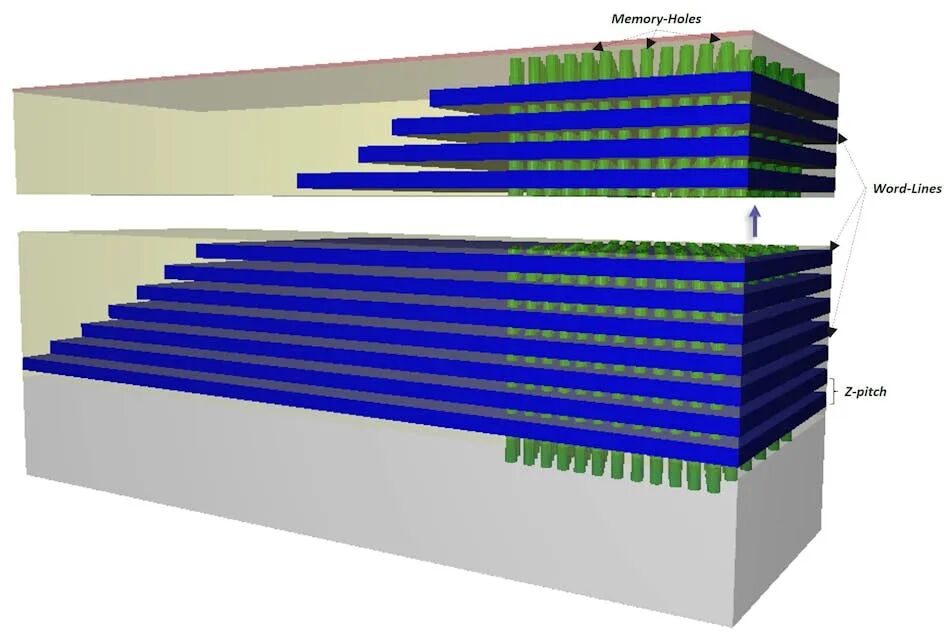

结果表明,带气隙的器件对相邻单元干扰更不敏感,通过在未选栅极施加“通电压”时阈值电压偏移更小得出此结论(图4)。该结果在测试器件上获得,该器件字线层有限,间距30 nm,存储孔直径80 nm。

4. 带气隙(左)和不带气隙(右)的电荷陷阱器件在不同通过电压下的阈值电压变化。

imec研究人员还发现气隙不影响内存性能和可靠性,耐久性可达1000次编程/擦除循环,与无气隙器件相当。基于此,孔侧气隙集成被认为是实现未来z轴间距缩放的关键步骤。

电荷陷阱切割:它在闪存未来发展中的地位

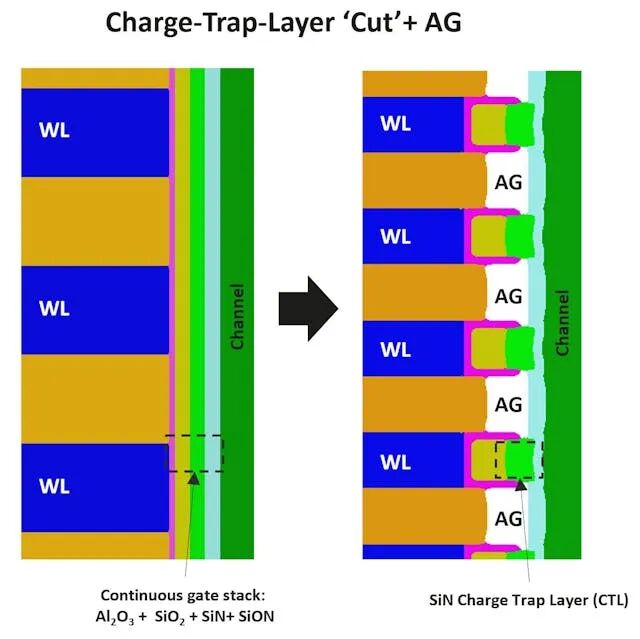

imec证明在栅极间介电层引入气隙可行,但目前存储单元中的空腔止于阻挡氧化层前。若将气隙引入阻挡氧化层和电荷陷阱层区域,仿真结果显示,电荷陷阱层分离可增大存储单元的存储窗口(图5),还能防止电荷横向迁移。

5. 连续栅堆叠(左)与具有电荷陷阱层切割和气隙集成的栅堆叠(右)之间的区别。

数据存储在闪存单元中,通过将阈值电压编程为不同电平实现。随着存储位数增加,所需电压电平数也增加,需要增加阈值电压总范围或减小相邻电平间隔。电荷陷阱削减技术可增加存储窗口,使每个存储单元存储更多位数。

但在3D NAND闪存中集成电荷陷阱切割并非易事,需要对极深且狭窄的孔壁进行定向蚀刻和沉积,目前imec正与供应商合作开发新技术。一旦电荷陷阱层可中断,imec打算将其与气隙集成方案结合,提供完整且可扩展的解决方案。

揭开3D NAND闪存的复杂性

随着半导体行业追求在更小空间存储更多数据,3D NAND闪存的Z轴间距缩小成为控制成本的关键。imec凭借技术专长和供应商生态系统,开发气隙集成和电荷陷阱消除等技术,支持缩小Z轴间距并保持存储器运行和可靠性。

同时,传统电荷陷阱单元架构收益放缓,存储器密度提升可能在本十年末趋于平缓。研究人员正研究更具创新性的单元架构,如将存储单元导电通道水平排列,或用沟槽式架构连接电荷陷阱存储单元,有望提高比特存储密度。

这些发展表明,研发中的技术将使存储器行业迈向100 Gb/mm²的数据存储,以满足云计算和人工智能应用的需求。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:imec,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com