HBM 4, 对决拉响

人工智能的火热,除了推动GPU的大红大紫外,HBM这几年背后的重要存储系统也冲上了舆论的漩涡。最近,SK Hynix和三星的表现和行动表明,HBM在未来取得了巨大的成就。

根据路透社的报道,HBM 当前,芯片占据了通用内存市场 去年的比例是15%, 8%。SK 海力士在 HBM 由于生成式式,市场占有最大的市场份额 AI 热潮刺激正确 Nvidia GPU 这个市场的需求急剧增加。这是占据 AI GPU 市场 80% 份额的 Nvidia 的 HBM3 唯一的内存供应商, 3 最新一代的量产月份开始量产。 HBM3E。在美光、三星等竞争供应商的发展中, HBM 为了阻止商品 SK 主导市场的海力士。

而且围绕HBM,厂商也各有各的招数。除对现有技术进行深度培育外,还围绕未来的HBM。 4.悄悄吹响攻击号角。另外,解释一下,因为作者没有找到更多关于HBM技术的介绍,所以本文没有提到他在HBM技术上的前景和分享,希望大家能补充一下。

坚持MR的SK海力士-MUF

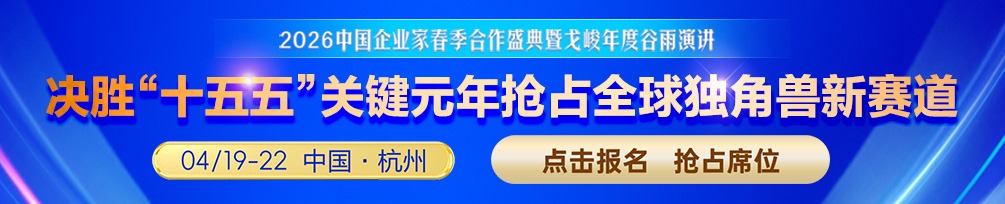

据SK 据hynix介绍,目前,封装技术已经超越了传统的“连接芯片电气,保护芯片免受外界冲击”的功能,但它已经成为实现差异化产品特性的重要技术。HBMSK海力士采用硅通孔技术(TSV:Through Silicon Via)、在批量回流模制底部添加充充充充充(MR-MUF:Mass Reflow-Molded Underfill)作为核心技术,先进的封装工艺赢得了卓越的市场声誉。

TSV技术在MR-MUF中很常见,批量回流焊接(MR)它是一种通过融化堆叠芯片之间的沉孔,使芯片相互连接的技术。在模塑底部添加充电(MUF)它是一种技术,可以在堆叠的芯片之间添加保护材料,从而提高耐久性和散热性。使用MR-MUF,可以同时封装多层 DRAM。

具体而言,从技术过程来看, DRAM 下面是连接芯片铅基的“沉孔”。MR 该技术涉及加热和熔化所有这些沉孔进行焊接。连接完所有 DRAM 之后,下一步将被称为 MUF 保护芯片的过程。注入具有优异散热性能的环氧密封胶,填充芯片间的缝隙,并将其封装。接着通过加热和加压使零件变硬,从而完成。 HBM。

SK海力士将这个过程描述为“将热量均匀地施加到烤箱中,并将所有芯片一次粘合,使其稳定高效。

SK最近的一个博客 Hynix高管表示,SK海力士致力于开发‘代表性存储产品’,以满足客户对性能、功能、尺寸、形状和功能的差异化需求,以满足AI时代的需要。为实现这一目标,公司正在推动TSV和MR-MUF的技术发展,这些技术在HBM性能中起着关键作用。

值得注意的是,虽然MR-MUF被广泛使用,但我们必须承认,MR-MUF 具有易翘曲、造成晶圆末端弯曲、空洞现象(即某些区域保护材料分布不均匀)也会对其进行处理 MR-MUF 稳定性产生不利影响等问题。但SK Hynix表示,与HBM开发初期相比,它们成功地减少了翘曲现象,目前我们正在开发技术来克服这个问题。下一步,选择将聚焦于减少间隙。

SK Hynix高管强调,该公司旨在完成“超越HBM的封装技术”任务。正如他所说,在短期内,我们的主要目标是扩大在韩国的生产能力,以满足HBM市场的需求。同时,我们应该充分利用世界各地的生产基地,实现利益最大化。从长远来看,我们的目标是保证先进的封装技术的开发和创新,就像MR-MUF技术目前是HBM的核心技术一样。

此外,SK Hynix也致力于芯粒。(Chiplet)及混和键合(Hybrid bonding)为了支持半导体存储器与逻辑芯片之间的异构集成,促进新型半导体的发展,等待下一代先进封装技术的发展。之中,Hybrid bonding也被认为是HBM封装的另一个新选择。但是根据之前的计划不同,SK海力士将在HBM为下一代做准备。 四中继续选用尖端封装技术MR-MUF。混合键合技术作为替代方案产生的预测,由于 HBM 放宽标准,慢慢介绍。

最近的一次技术会议上,SK Hynix分享说,下一代封装技术正朝着存储器、逻辑和控制器相结合的方向发展,比如2.5D,同时,SK海力士也使用这些技术。 HBM 更加稳健。

谈到HBM的未来,SK Hynix认为,市场将更加系统化(Specialized)和定制化(Customized)为了满足客户的需求,商品。他强调,对于新一代HBM来说,卓越的性能是基本条件,同时必须具备满足不同客户特定需求、超越传统存储特性的优势。

此外,SK 早些时候,海力士公司还与台积电合作 (TSMC) 签署谅解备忘录 (MoU),与下一代合作开发 HBM,并且通过先进的封装技术增强逻辑和 HBM 集成。

通过这一举措,公司计划继续开发 HBM4,即 HBM 第六代商品系列,预计将于 2026 2008年开始量产。

SK海力士表示,AI存储领域的全球领导者与台积电的合作将为HBM技术带来更多的创新。此次合作有望通过产品设计、代工和内存提供商之间的三面合作,实现内存性能的突破。

两家公司将首先致力于升级安装。 HBM 基本芯片性能封装底部。HBM 制作方法是核心 DRAM 采用芯片堆叠 TSV(硅通孔)技术的基本芯片,并且使用 TSV 将 DRAM 在堆栈中,固定数量的层直接连接到 TSV 形成关键芯片 HBM 封装。底部的基础芯片连接到控制 HBM 的 GPU。

SK海力士使用专有技术制造高达HBM3E的基础芯片,但为了将附加功能封装在有限的空间内,计划在HBM4基础芯片上选择台积电的先进逻辑技术。这也有助于 SK 定制海力士生产 HBM,满足客户对性能和效果的普遍需求。

同时,SK海力士和台积电也同意与SK海力士的HBM和台积电的CoWoS(基板上的晶圆芯片)技术进行合作,以满足常见客户对HBM的需求。

SK 海力士总裁兼 AI Justinn基础设施负责人 Kim说:“我们希望与台积电建立强大的战略伙伴关系,以帮助我们加快与客户的开放合作,开发行业内最好的性能。 “HBM4。”“通过这次合作,我们将进一步巩固作为整体人工智能内存提供商的市场领导地位,通过增强定制内存平台领域的竞争力。”

多年来,台积电和 SK 海力士建立了稳定的战略伙伴关系。我们共同努力,整合最先进的逻辑和最先进的逻辑 HBM,提供世界领先的人工智能解决方案 。"台积电的Kevin “展望下一代,Zhang。” HBM4,我们相信,我们将继续密切合作,为我们的共同客户提供最佳的集成解决方案,创造新的人工智能创新。

三星考虑混合键合

和SK 不像Hynix,三星使用的TC在HBM封装上是不同的。-NCF(thermal compression with non-conductive film),即非导电膜热压缩。

就技术而言,这是一种不同于MR-MUF的技术。每一次堆叠芯片时,都要在每一层之间放置一层不导电的粘合膜。这种薄膜是一种聚合物材料,用来保护芯片彼此绝缘,保护节点免受碰撞。随著三星的发展,三星越来越少 NCF 材料厚度,将 12 层第五代 HBM3E 厚度降到 7 μm (μm)。该公司表示:“这种方法的优点是可以随着层数的增加和芯片厚度的减小而最大限度地减少翘曲,使其更适合构建更高的堆栈。”

根据三星的介绍,TC NCF方法在堆叠更高层次方面具有优势。但是对这种技术来说,提高热量和压力是其成功的关键。所以据报道,为了进一步提高其标新,三星之前正在与设备制造商进行讨论。面临SK海力士的竞争,三星电子在全公司范围内集中力量,并于2月宣布“Advanced TC-NCF”技术。这种技术可以减少 TC-NCF 过程中需要薄膜的厚度,进而保证薄膜的厚度。 HBM 在增加半导体层数的同时非常高。

另外,有消息称,三星的TC NCF的良率不如SK hynix,所以三星电子考虑在穿硅电极中引入MUF材料(TSV)工艺中。报告指出,三星还从日本购买了硬化(成型)设备,可使这类MUF变硬。补充一下,在第二代HBM之前,SK海力士也使用了NCFM。 ,但是从第三代(HBM22E)开始使用MUF(特别是MRF)-MUF)。分析人士甚至认为,MUF是SK海力士能够在HBM市场脱颖而出的原因,这就是为什么有消息称三星也在寻找开发和引进这项技术。一位熟悉三星情况的半导体行业高管表示,“据我所知,三星正在研究的。 MUF 材料和 SK 海力士的技术也不一样。

之后,三星对此传言并指出,该公司将继续在TC工作。 在NCF上发力。三星甚至在日前的一个博客中分享了他们对未来的看法。

三星强调,当被问及为什么公司目前的HBM如此与众不同时,该公司正在AdvancedTCed中 NCF上的观点是不可或缺的。三星方面继续说,HBM 选用 DRAM 垂直堆叠芯片(例如 8H 和 为了提高容量和带宽,12H。但是,不同的一代 HBM 全部遵循预定的整体厚度。在这种限制下,随着附加层的堆叠,负责数据存储的关键裸片不可避免地会变薄,这可能会给组装带来挑战,导致芯片翘曲或破裂,热阻增加。

对三星来说,HBM 三星拥有完善的高密度堆叠芯片控制技术,主要受芯片间隔的影响,降低芯片间NCF材料厚度,利用热压缩技术使芯片更加紧密。这是行业内最小的创新方法。 7 μm (um) 芯片间隔。另外,在芯片键合过程中,三星策略性地制定了需要数据传输的小沉孔和散热特别重要的大沉孔。这样提高了排热和产量。另外,在有限的封装尺寸内,应用生产工艺最小化单个封装尺寸。 DRAM 芯片尺寸,保证了优良的量产能力和可靠性,从而提供了显著的竞争优势。

与此同时,三星也提到,业界越来越意识到,处理器和内存公司不足以释放自己的独立努力来提高自己的产品。 AGI 创新是时代所需要的。所以,“定制” HBM“成为一种趋势,这也代表了实现处理器与内存协同优化以加速这一趋势的第一步。所以,三星在内存、代工、系统LSI、先进封装等方面都有综合能力。另外,三星也是下一代。 HBM 成立了一个特殊的团队,利用公司前所未有的能力,我们致力于在未来的塑造上做出重大改变。

三星在谈到未来的计划时表示,HBM 市场还处于起步阶段,预计会迅速发生变化。公司的战略是通过预测市场发展,提前积极规划和开发必要的产品来保持领先水平。随着 HBM 随着市场的成熟,三星预计三大变化将重塑行业:

第一,“细分”。是的 HBM 在早期阶段,硬件需要多功能。但是,随着服务围绕杀手级应用的不断发展,硬件基础设施不可避免地会优化每一项特定服务。为应对这一趋势,三星将提供一系列封装选项(8H、12H 和 16H)与基础芯片相结合,对核心芯片进行标准化。

其次,处理器和内存之间的协同优化需要更高水平的定制。为了应对这一挑战,三星将利用创建平台最大限度地利用它 HBM 通过扩大我们的生态系统战略伙伴关系,解决方案中的通用设计元素,并制定一个高效的系统,以满足定制要求。

三是为克服“电源墙”,处理器与内存之间的距离将变得更近。首先是创新 HBM4 显然,它在其基本芯片中采用了逻辑处理技术。其次,随着当前的创新, 2.5D 到 3D HBM 结构的变化发生了,而第三次创新涉及集成 DRAM 单元与逻辑,这就是设计 HBM-PIM 的方法。三星为了把这些创新变成现实,在积极规划和准备推动市场的同时,也开始与客户和合作伙伴进行讨论。

三星强调,随之而来 HBM 作为生成式 AI 不可否认的是,许多用户和数据中心正在迅速选择最优化内存解决方案的地位。但是,确保人工智能服务不间断尤为重要。,即便是有缺陷的芯片也会产生灾难性的影响。因此,保证 HBM 质量设计与检测技术势在必行。另外,开发可以进一步降低功耗,提高系统能效。 HBM 设计结构也很重要。

所以三星计划将16H技术融入下一代HBM4,针对高温环境优化的NCF组装技术和尖端生产工艺。根据三星的计划,HBM 样品将于2025年生产。

然而,三星副总裁 Kim Dae-woo 早些时候,三星在韩国的一次会议上表示,三星正在考虑进入HBM。 4应用混合键合或NCF,并于2026年开始量产。混合键合更有优势,因为它可以紧凑地添加更多的堆叠,而无需使用添加沉孔连接硅通孔。 (TSV)。运用相同的技术,HBM 上面的核心芯片 DRAM 还能变得更厚。

Kim 也强调,在多 8 个堆叠时,MR-生产效率比MUF TC-NCF 更高,但是一旦达到堆叠, 12 一个或多个,后者会有更多的优势。副总裁还指出,当时 HBM4 在推出时,定制请求有望增加。他补充说,缓冲芯片将成为逻辑芯片,所以芯片可以来自三星或台积电。

还有报道指出,英伟达还将选择三星技术,制作HBM封装,这对这个韩国巨头来说,是另一个好消息。

最新的台积电封装技术帮助战斗

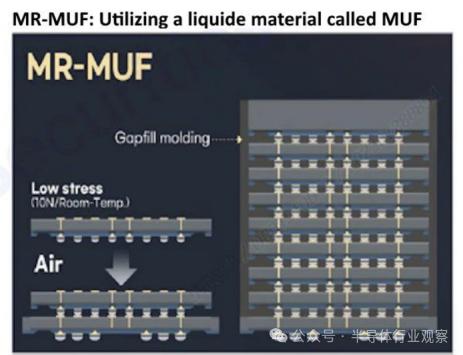

该公司在北美技术研讨会上推出了下一代晶圆系统平台——CoW-SoW——这个平台将实现晶圆级设计。 3D 集成。这项技术是基于台积电的 2020 年推出的 InFO_SoW 在晶圆级系统集成技术的基础上,该技术可以构建晶圆级逻辑Cpu。到目前为止,只有特斯拉在其中。 Dojo 该技术在超级计算机中得到了应用,台积电表示该计算机已经投入生产。

即将推出的 CoW-SoW 台积电将在其晶圆系统平台上合并两种封装方式。——InFO_SoW 集成芯片系统 (SoIC)。使用晶圆上芯片 (CoW) 该方法可以将存储器或逻辑直接堆叠在晶圆上系统上。预计2027年将实现新的CoW_SoW技术的大规模生产,但是实际产品何时上市还有待观察。

据悉,台积电的CoW-SoW致力于将晶圆级Cpu与HBM4内存融为一体。下一代内存堆栈将采用 2048 位置接口,这使得将 HBM4 在逻辑芯片顶部直接集成是可能的。与此同时,将额外的想法堆积在晶圆级Cpu上,以优化成本也是有意义的。

台积电业务开发副总裁Kevin:“因此,在未来,我们的客户将使用晶圆级集成[允许]来整合更多的逻辑和存储器。 Zhang说。“SoW 不再是虚构的;我们已经与客户合作生产了一些已经到位的商品。在我们看来,通过使用我们先进的晶圆集成技术,我们可以为客户提供至关重要的产品,使他们能够继续提高能力,为他们的人工智能集群或[超级计算机]引入更多的计算和节能计算。”

一般而言,晶圆级Cpu(即晶圆级Cpu Cerebras 的 WSE),尤其是基于 InFO_SoW 处理器可以提供显著的性能和效率优势,包括高带宽和低延迟的关键到核心通信、低功率传输网络阻抗和高能效率。这种Cpu作为额外的优势,也有额外冗余的“额外”核心模式。

然而,InFO_SoW技术有一定的局限性。例如,使用这种方法制造的晶圆级Cpu完全依赖于电影上的存储器,这可能不能满足未来人工智能的需求(但目前很好)。CoW-SoW 这一问题将得到解决,因为它将被允许。 HBM4 把它放在这种晶圆上。此外,InFO选择单节点加工的SoW晶圆,该节点不支持3D堆叠,而CoW-SoW商品则支持3D堆叠。

参考链接

https://news.skhynix.com.cn/top-team-insights-motto-of-package-and-technology-head-woojin-choi/

https://semiconductor.samsung.com/news-events/tech-blog/the-perfect-harmony-created-by-samsung-hbm-powering-the-ai-era/

https://www.tomshardware.com/tech-industry/tsmc-to-go-3d-with-wafer-sized-processors-cow-sow-system-on-wafer-technology-allows-3d-stacking-for-the-worlds-largest-chips

https://www.eetasia.com/sk-hynix-and-tsmc-ink-mou-on-hbm-technology/

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:编辑部,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com